32

- ELETTRONICA OGGI 430 - SETTEMBRE 2013

te generazione di SerDes. Per esempio le funzionalità di

equalizzazione adattiva come il controllo di guadagno

automatico, l’equalizzazione lineare continuos-time e lo

sliding DFE permettono di mantenere un bit-error rate

particolarmente contenuto e permettono ai transceiver

SerDes UltraScale di gestire direttamente backplane ad

alta velocità e prestazioni di diversi GHz.

L’architettura UltraScale offre diverse soluzioni inte-

ressanti dal punto di vista dell’interfacciamento con la

memoria.

Integra infatti diversi core hard-IP per controller SDRAM

di tipo DDR3 e DDR4 e blocchi hardened per il DDR

physical layer (PHY). In pratica è stato incrementato il

numero di controller SDRAM hard-IP, mentre le porte

per la SDRAM sono più ampie e più veloci.

I blocchi hardened PHY per la SDRAM sono in grado di

ridurre la latenza di circa il 30% rispetto a soluzioni PHY

di tipo soft-core, mentre la capacità di gestire memorie

SDRAM di tipo DDR4 permette anche di ridurre i consu-

mi di circa il 20%.

Le performance del BRAM (la Block-RAM on chip) sono,

inoltre, state adattate per adeguarsi a quelle degli altri

blocchi del sistema all’abbassamento dei consumi di

energia. Una nuova funzionalità, infine, permette la

realizzazione di grandi e veloci array di RAM senza la

necessità di logica aggiuntiva o di risorse di routing.

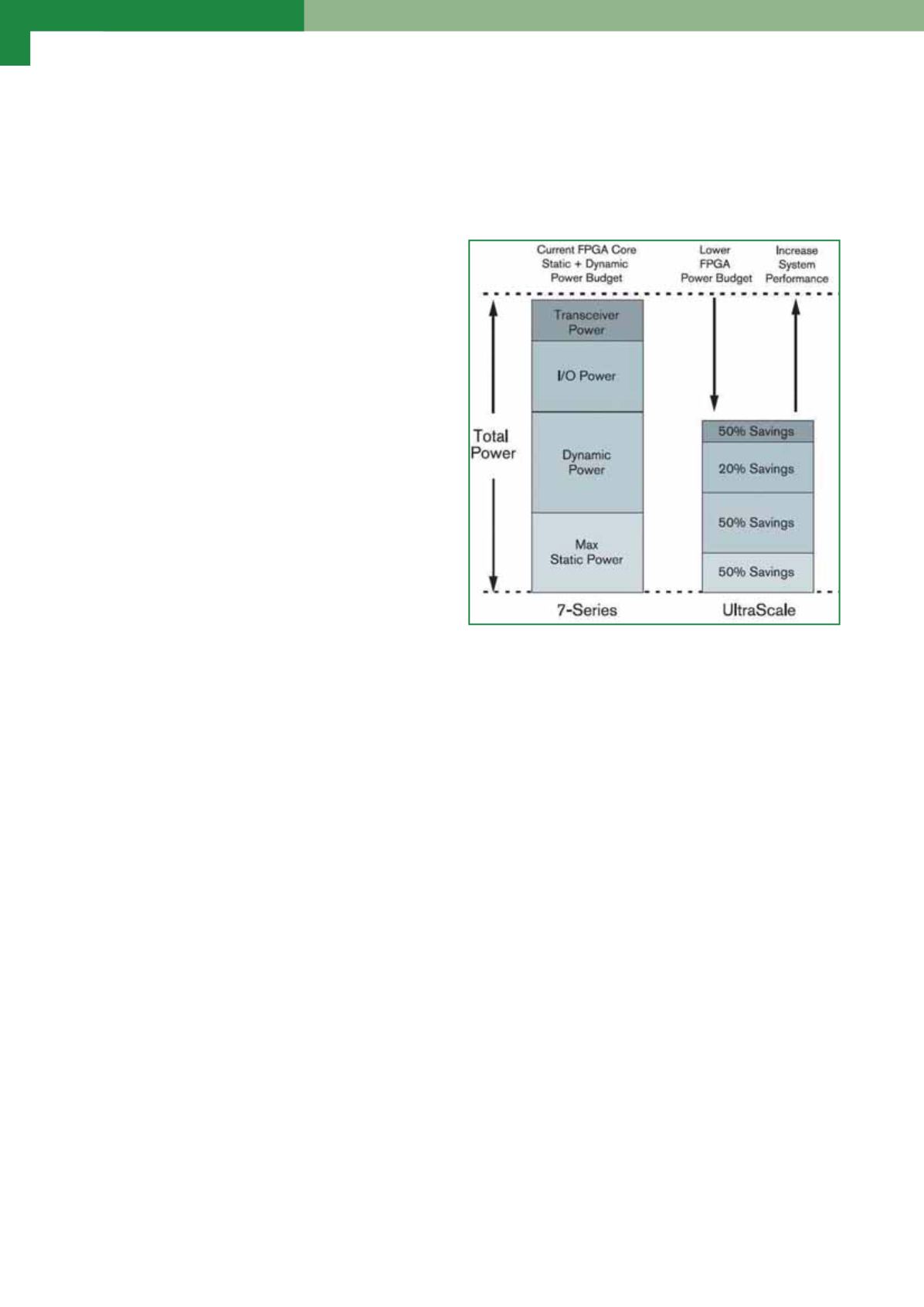

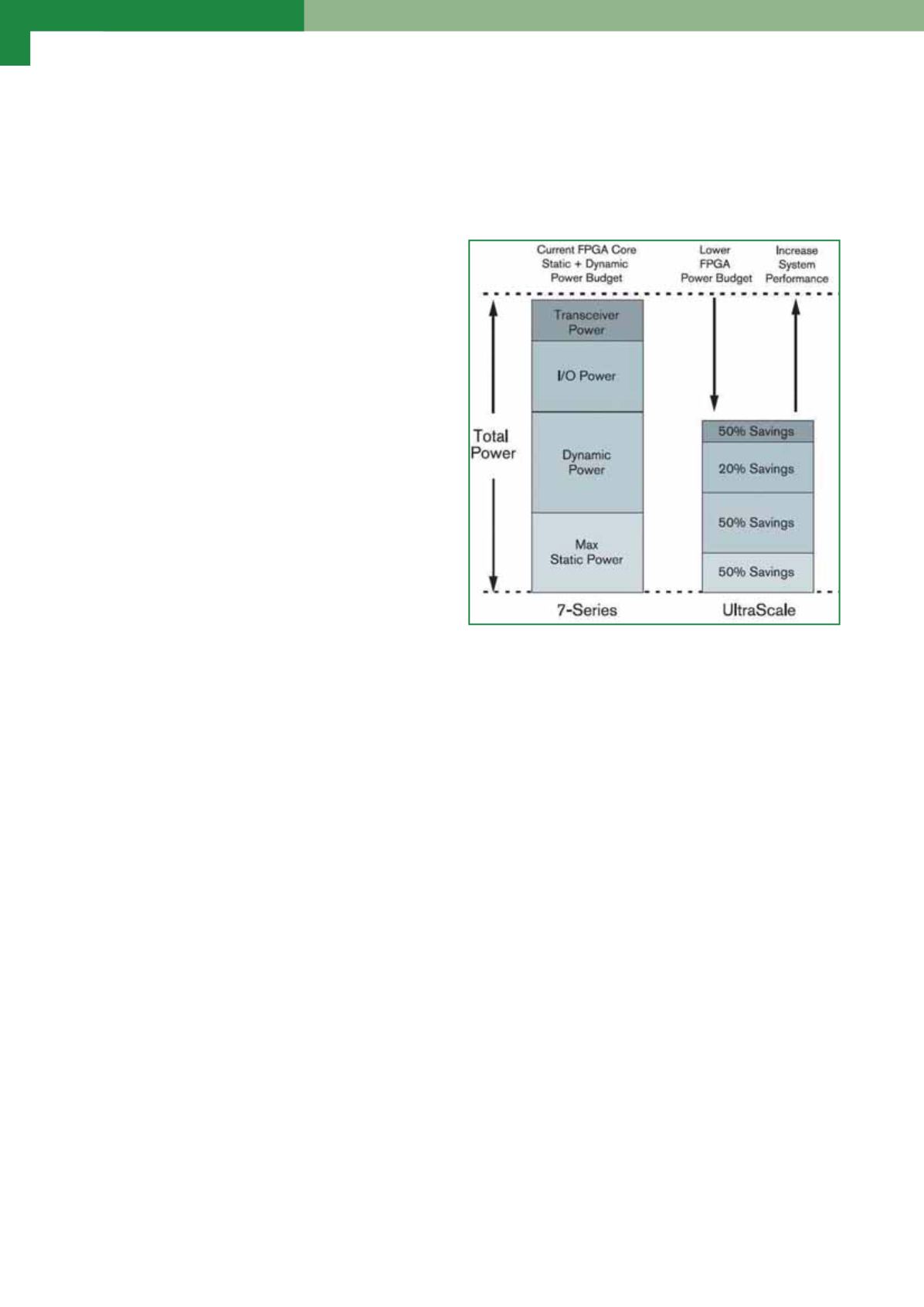

Il power management

La gestione dei consumi è un elemento ormai imprescin-

dibile per qualunque device. Anche questa architettura

utilizza diverse tecniche su questo versante e permette

di ridurre sensibilmente i consumi. I dati dichiarati da

Xilinx sono infatti un risparmio complessivo di circa il

50% dei consumi del sistema rispetto ai componenti

della generazione precedente, la serie 7.

L’architettura UltraScale permette infatti di ridurre del

50% i consumi di sezioni come i transceiver, e di circa

il 20% quelli necessari all’I/O. Parte del merito di questi

risultati è legato all’utilizzo di semiconduttori low power

e a specifiche tecniche software.

Dal punto di vista del processo produttivo, l’architet-

tura UltraScale è stata progettata per essere utilizzate

con diverse tecnologie. Xilinx ha infatti collaborato con

TMSC per sviluppare i processi a 20 nm per permettere

la realizzazione dei primi componenti con architettura

UltraScale.

I primi dispositivi UltraScale estenderanno le famiglie

di FPGAVirtex e Kintex ora basate sulla tecnologia di

processo da 28 nm, e serviranno come base per i futuri

SoC Zynq UltraScale.

Questa architettura però trarrà benefici ancora maggio-

ri dalla generazione di processo successiva di TMSC,

quelle a 16nm grazie anche al programma di sviluppo

“FinFAST” di Xilinx. Il primi prodotti con questa nuova

generazione di processo produttivo a 16 nm dovrebbe-

ro arrivare nel 2014.

L’ottimizzazione di Vivado

Un aspetto fondamentale per lo sviluppo di nuovi

device riguarda la disponibilità di tool adeguati. Con i

device Xilinx della serie 7 è stata introdotta al Vivado

Design Suite per lo sviluppo di prodotti completamente

programmabili, e questo tool è valido anche per la pro-

gettazione con l’architettura UltraScale. Tra le caratteri-

stiche più interessanti di questa suite c’è la possibilità

di intervenire sui principali colli di bottiglia relativi alla

progettazione e implementazione dei sistemi program-

mabili. L’ottimizzazione fra l’architettura UltraScale e

la suite Vivado permette, in base ai dati di Xilinx, una

utilizzazione dei dispositivi superiore al 90% senza

degrado nelle prestazioni

La Vivado Design Suite con il supporto agli FPGA basati

su architettura UltraScale è disponibile attualmente

per i primi clienti, mentre i primi dispositivi UltraScale

saranno disponibili nel quarto trimestre 2013.

Q

TECH INSIGHT

ULTRASCALE

Fig. 3 - Il risparmio complessivo di energia dell’architettura UltraScale

rispetto alla serie 7 Xilinx