29

- ELETTRONICA OGGI 429 - LUGLIO/AGOSTO 2013

ANALOG/MIXED SIGNAL

JESD

Chip per la conversione

dati su interfacce seriali

ad alta velocità

N

egli ultimi anni si sono viste le

interfacce seriali affermarsi sem-

pre più prepotentemente rispetto a

ogni sorta di collegamento in paral-

lelo. Fra i molti vantaggi che offrono

ci sono sicuramente la semplicità del

layout e le ridotte dimensioni sul sili-

cio, ma non va sottovalutata la mag-

gior versatilità nella configurazione

delle regole di instradamento delle

linee dedicate ai segnali da conver-

tire o dopo la conversione. Inoltre,

rispetto alle connessioni multiple in

parallelo, i collegamenti seriali offrono

maggior protezione nei riguardi del

rumore elettromagnetico e riescono

a isolare più efficacemente i circuiti

analogici e quelli digitali che oggi si

trovano sempre più ravvicinati tanto

sul silicio quanto sulle schede stam-

pate. D’altro canto, si sta assistendo

anche a un ulteriore proliferarsi dei

sottosistemi per l’elaborazione dei segnali multimediali com-

posti da convertitori multipli A/D o D/A in parallelo allacciati

a un pari numero di processori DSP grazie al supporto di

Fpga con dimensioni adeguate a sostenere in parallelo tutti i

collegamenti necessari al caso. Invero, è proprio l’architettura

di base degli Fpga ad aver invogliato i progettisti a implemen-

tare il tutto in parallelo, ma questo approccio sta cambiando

proprio da quando sono disponibili sul mercato le nuove tec-

nologie di interfacciamento seriale ad alta velocità. Ed è pro-

prio questa la motivazione che spinse il consorzio Jedec, Joint

Electron Devices Engineering Council, a definire nel 2006

lo standard JESD204 che permetteva di raccogliere in una

singola linea seriale i

segnali in transito fra

i convertitori e gli I/O

dell’Fpga fino alla velo-

cità massima di 3,125

Gbps con una tensione

di modo comune com-

presa fra 0,72 e 1,23 V

e un’escursione picco-

picco per i simboli di

800 mV.

Il pregio di queste

innovative interfacce

seriali ad alta veloci-

tà consisteva proprio

nell’accontentarsi di

due fili e perciò riusci-

re con un solo doppino

a collegare efficace-

mente un parallelo di

convertitori A/D o D/A

ai loro rispettivi DSP

all’interno dell’Fpga eliminando in un sol colpo fino a 16

linee Cmos o 32 linee Lvds tipicamente utilizzare dai moduli

Serdes degli Fpga in quella particolare applicazione. Grazie

a ciò rimangono parecchi pin liberi sull’Fpga che possono

essere impiegati in altro modo e, inoltre, rispetto all’architet-

tura parallela diminuiscono nettamente i consumi oltre alle

dimensioni e si semplifica il lavoro di ottimizzazione da tutti

i punti di vista, sia hardware che software. Nel 2008 è stata

rilasciata la seconda revisione dello standard denominata

JESD204A nella quale viene adottata la modulazione in qua-

dratura che perciò permette di multiplexare più trasferimenti

da 3,125 Gbps ciascuno in un unico collegamento seriale.

Lucio Pellizzari

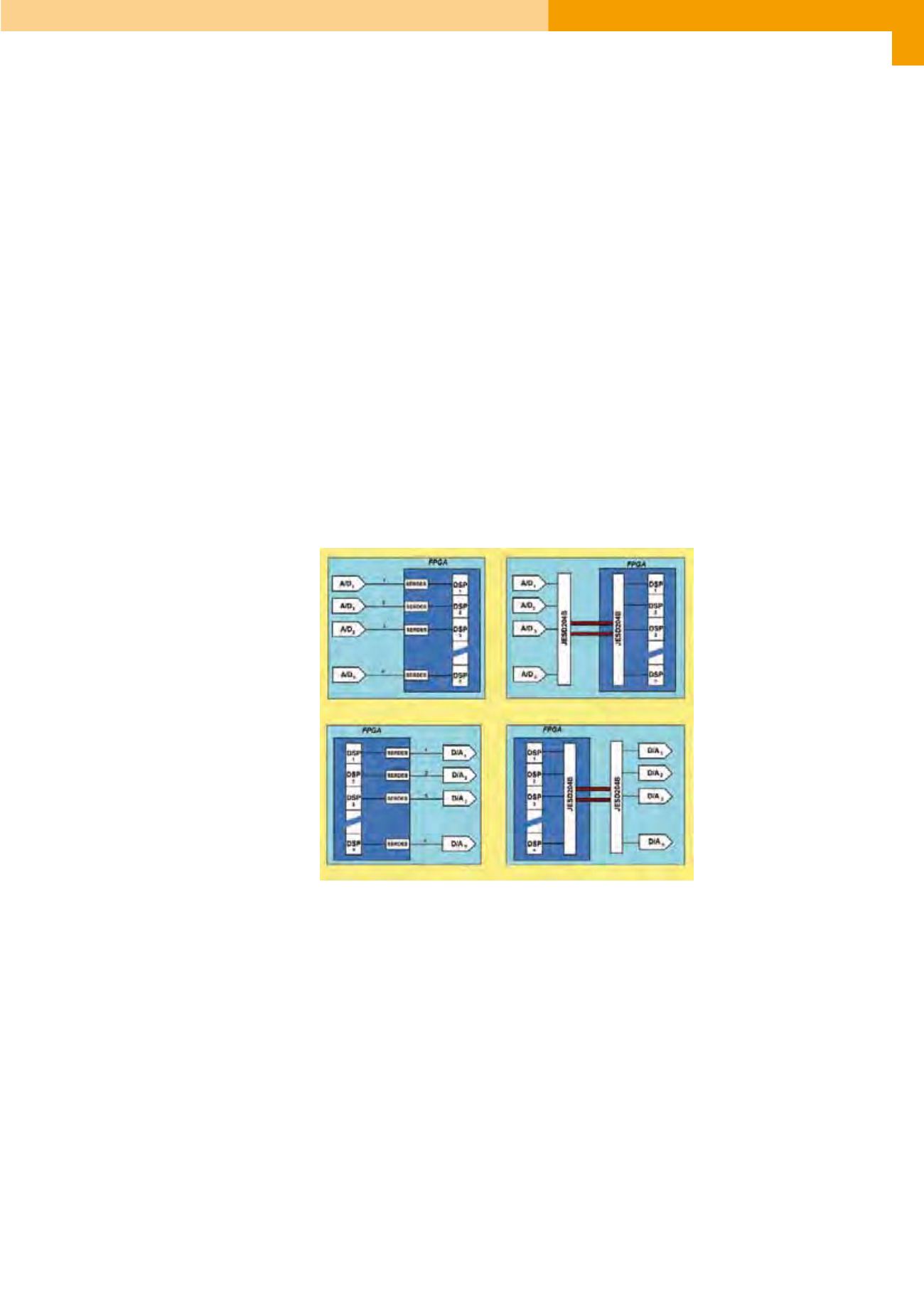

Per connettere gli array di core DSP interni agli

Fpga con i convertitori periferici A/D o D/A si

può fare a meno dei tradizionali e ingombranti

collegamenti in parallelo grazie alle nuove

interfacce seriali ad alta velocità JESD204A/B

Fig. 1 – Le interfacce seriali JESD204B offrono collegamenti più

semplici, veloci ed efficienti fra i moduli dei grandi Fpga riducendo

i consumi e le dimensioni sul silicio