9

NATIONAL INSTRUMENTS

LA COPERTINA DI EMBEDDED

EMBEDDED

60 • MAGGIO • 2016

impiegati sia per eseguire elaborazioni con grandi volumi

di dati, sia per le misure dei sensori ad alta velocità. I di-

spositivi, inoltre, hanno una latenza estremamente bassa,

fondamentale per le applicazioni di visione. La latenza, in-

fatti, incide sul tempo che trascorre prima di prendere una

decisione basata sui dati delle immagini. Gli FPGA posso-

no contribuire a evitare il jitter e, di conseguenza, fungere

da unità di elaborazione altamente deterministiche.

La creazione di un sistema eterogeneo con un FPGA,

tuttavia, mette i progettisti di sistemi davanti a sfide

di programmazione importanti. Mentre il time to mar-

ket fa pressioni sul supporto, i progettisti di sistemi di

visione devono riuscire a creare rapidamente un pro-

totipo di una soluzione con caratteristiche complesse.

La programmazione sui sistemi eterogenei richiede

uno strumento in grado di aiutare gli esperti del setto-

re a progettare le funzioni IP (Intellectual Property) su

più piattaforme e testare l’algoritmo di visione prima di

compilarlo ed eseguirlo sull’hardware di destinazione.

Questo strumento permetterebbe l’accesso facile al throu-

ghput e alle informazioni sull’utilizzo delle risorse du-

rante tutto il processo di prototipazione. Qui NI descrive

l’ingegneria dell’algoritmo, quel processo grazie al quale

l’esperto può trovare la risoluzione del problema a porta-

ta di mano, senza preoccuparsi della tecnologia hardware

sottostante. NI VisionDevelopment Module con Vision As-

sistant offre questa opportunità.

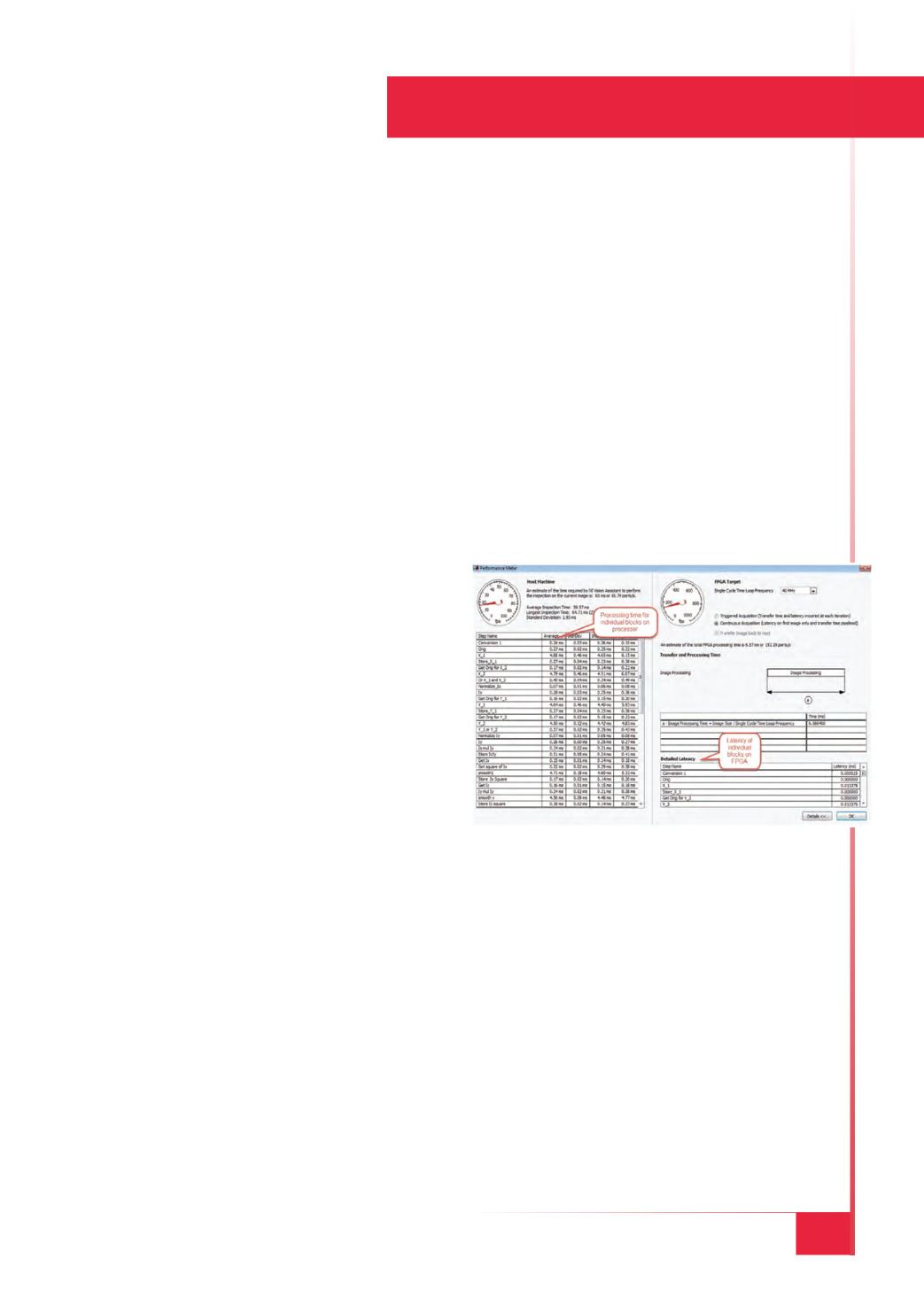

NI Vision Development Module, con Vision Assistant,

consente una prototipazione e una generazione del codice

rapide, la stima delle risorse FPGA, la parallelizzazione

automatica del codice e la sincronizzazione dei flussi pa-

ralleli (per attività come il bilanciamento della latenza).

NI Vision Development Module include più di 50 funzioni

FPGA per l’elaborazione delle immagini e le funzionalità

per trasferire le immagini in modo efficace tra il proces-

sore e l’FPGA. Vision Assistant all’interno di Vision De-

velopment Module può essere impiegato per una prototi-

pazione rapida e per lo sviluppo di applicazioni di visione

FPGA.

Prototipazione basata sulla configurazione

Vision Assistantè uno strumento di prototipazione ba-

sato sulla configurazione, che consente di eseguire ite-

razioni sugli algoritmi di elaborazione delle immagini

e comprendere come i cambiamenti nei parametri in-

fluenzino le immagini. Con Vision Assistant è possibile

visualizzare il risultato (l’immagine elaborata) dopo ogni

blocco di visione in una pipeline di immagini (Fig. 1).

Può essere utilizzato per testare algoritmi e parametri

differenti su più serie di immagini, senza dover compilare

l’IP, riducendo così notevolmente il tempo necessario per

progettare l’algoritmo di visione.

NI ha personalizzato il tool per gestire le esigenze dei pro-

grammatori FPGA. Nella realizzazione di un algoritmo su

FPGA, le preoccupazioni principali riguardano il consumo

delle risorse dell’FPGA, la latenza della pipeline e la fre-

quenza massima che l’algoritmo può raggiungere su una

specifica struttura. Vision Assistant offre una stima delle

risorse impiegate in ciascun blocco nella pipeline delle im-

magini. Si può usare per testare i risultati degli algoritmi

nell’ambiente di prototipazione e nel codice distribuito,

garantendo così che l’implementazione produca gli stessi

risultati. Un’altra considerazione riguarda le dimensioni

del kernel da utilizzare per l’operazione di filtraggio delle

immagini. La scelta delle dimensioni del kernel influen-

za l’impiego delle risorse e la latenza nella pipeline; un

kernel di dimensioni maggiori, solitamente, richiede più

risorse rispetto a uno più piccolo. Per scegliere le dimen-

sioni del kernel più adatte all’applicazione è possibile uti-

lizzare Vision Assistant, che permette di fare esperimenti

fino al raggiungimento delle migliori prestazioni, con un

consumo minimo delle risorse e il massimo rendimento.

Una stima in tempo reale delle funzioni dell’IP di visione,

come mostra la figura 1, è utile durante la prototipazione.

L’esecuzione in parallelo di più pipeline di immagini è un

requisito comune. Scenari simili impongono che, dall’unio-

ne delle diverse pipeline in una singola pipeline, la latenza

delle pipeline parallele debba essere bilanciata. NI fornisce

un buffer di sincronizzazione nel toolset dell’IP di visione

FPGA. Vision Assistant calcola automaticamente le laten-

Fig. 2 – Utility di monitoraggio delle performance