EMBEDDED

54 • NOVEMBRE • 2014

44

HARDWARE

HSR

di schede sono equi-

paggiate con oscillatori

molto diversi da loro;

questi ultimi possono

essere fissi o regolabili

e caratterizzati da valori

di accuratezza e range

di frequenza molto dis-

simili tra loro. In que-

sto caso il periodo di

clock è necessario per

il blocco di commuta-

zione HSR. In funzione

dell’implementazione,

il periodo di clock può

essere fornito anche

ai chip PHY corredati

di funzionalità IEEE

1588, ai MAC Ethernet

e ad altri blocchi che

richiedono una tempo-

rizzazione accurata, ad

esempio per la marca-

tura temporale (time

stamping) delle misure

dei valori campione.

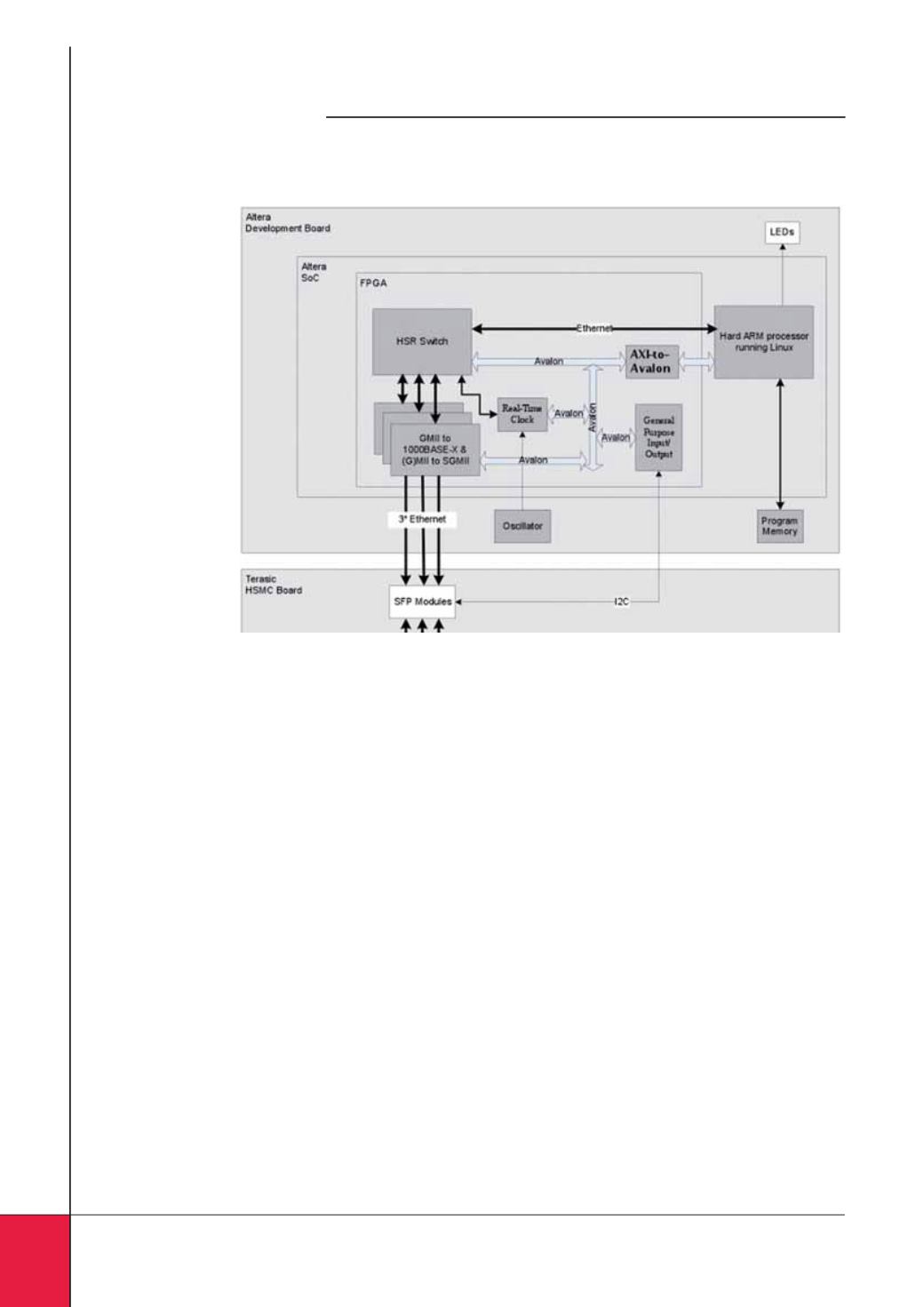

La struttura di commutazione Avalon collega i blocchi al pro-

cessore ARM di tipo hard attraverso il bridge AXI-Avalon.

Di utilizzo molto comune e basato su uno standard aperto,

Avalon rappresenta la scelta ideale per l’implementazione de-

gli accessi ai registri interni dell’FPGA. Il processore esegue

il monitoraggio e il controllo delle funzionalità dei blocchi

connessi attraverso Avalon mediante l’accesso ai registi di

Avalon. Per esempio, esso effettua il monitoraggio in modo

continuo della velocità di interfacciamento dei moduli SFP

per connessioni in rame, mediante un’interrogazione ciclica

(polling) del chip PHY presente all’interno del modulo. Nel

momento in cui cambia la modalità, il processore configura

in modo appropriato la velocità dell’adattatore (G)MII-SG-

MII e della porta dello switch HSR.

Implementazione pratica di HSR…

Poiché la topologia tipica di una rete HSR è del tipo ad anel-

lo, in generale il numero di salti (hop) tra la sorgente e la

destinazione sarà maggiore rispetto a quello delle topologie

Ethernet tradizionali. Per questo motivo i requisiti di latenza

di inoltro (forward latency) dei dispositivi sono così ridotti

da rendere praticamente impossibile l’implementazione di

un nodo HSR con un engine di inoltro basato su software.

Poiché HSR è una tecnologia relativamente nuova e in conti-

nua evoluzione, le realizzazioni sono basate su blocchi IP im-

plementati mediante FPGA. A questo punto val la pena sotto-

lineare che HSR è fondamentalmente basata sui concetti tipi-

ci di Ethernet, ragion per cui le reti HSR adottano parecchie

tecnologie mutuate dalle tradizionali reti Ethernet, come ad

esempio LAN virtuali e assegnazione di priorità. L’implemen-

tazione interna di uno switch HSR, con le sue funzionalità di

apprendimento degli indirizzi e le code in uscita multiple, è

dunque molto simile a quella degli classici switch Ethernet.

Un’implementazione HSR, d’altro canto, non può essere sola-

mente di tipo hardware.

A causa della ridondanza, non è possibile individuare singo-

li guasti della rete senza ricorrere a un protocollo specifico

denominato protocollo di supervisione HSR. Quest’ultimo

protocollo controlla gli altri nodi della rete HSR, i numeri

di sequenza dei loro frame di supervisione e identifica le

porte ridondanti che ricevono i frame, memorizzando le in-

formazioni in una tabella denominata tabella dei nodi (no-

des table). Queste informazioni possono essere impiegate

per localizzare i link non funzionanti correttamente e altri

problemi della rete. Per ragioni pratiche, questo protocollo

relativamente complesso non può essere implementato in

hardware, bensì in software. Vista la necessità di far ricorso

a risorse hardware e software per l’implementare di una rete

HSR, un SoC permette di realizzare una soluzione HSR sfrut-

tando un unico chip.

Fig. 2 – Schema a blocchi delle due schede