EMBEDDED

54 • NOVEMBRE • 2014

42

HARDWARE

HSR

l termine “smart grid” identifica

una moderna rete elettrica che

sfrutta un certo numero di nuove

tecnologie per la raccolta di infor-

mazioni, la comunicazione e il

controllo della rete stessa.

Oltre a garantire una migliore efficienza e una

maggiore affidabilità, una smart grid consente

una generazione distribuita dell’energia, sem-

plificando il collegamento di sorgenti di energia

rinnovabili diversificate, come ad esempio l’energia fotovol-

taica o quella eolica, alle rete. Tra le nuove tecnologie impie-

gate nelle smart grid di possono segnalare i protocolli HSR

(High -Availability Seamless Redundancy) e IEEE 1588 PTP

(Precision Time Protocol) utilizzati nelle sottostazioni per la

comunicazione interna e la sincronizzazione temporale delle

misure elettriche.

In questo articolo è proposta l’implementazione dei proto-

colli HSR e IEEE 1588 PTP mediante il SoC Cyclone V di

Altera su cui gira il sistema operativo Linux. Il chip integra

una struttura FPGA e un processore hard basato su ARM.

La soluzione proposta può essere usata sia per lo sviluppo

di nuovi progetti sia per l’aggiornamento di dispositivi esi-

stenti.

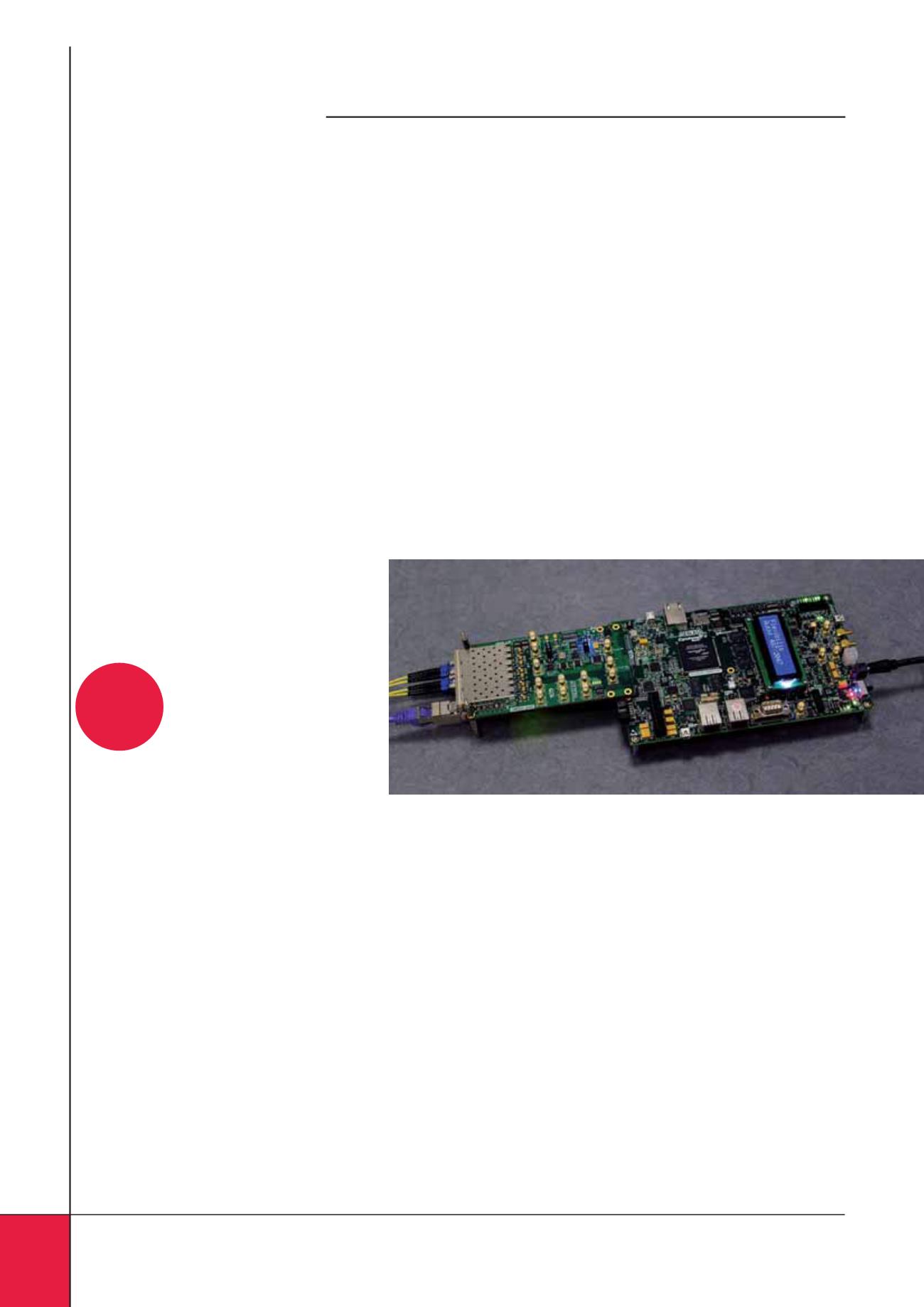

Nella figura 1 è riportato un esempio di implementazione dei

protocolli HSR e IEEE 1588 PTP che sfrutta un SoC della

serie Cyclone. Nella figura sono rappresentate due schede

PCB, entrambe già disponibili: quella di maggiori dimensio-

ni è la scheda di sviluppo Cyclone V SX di Altera, mentre

quella di dimensioni inferiori è la scheda SFP-HSMC di Te-

rasic che si collega al connettore HSMC della scheda SoC e

mette a disposizione slot SFP (Small Form-factor Pluggable)

per collegamenti Ethernet in fibra o in rame, in funzione del

tipo di modulo. Nella figura 2 è riportato lo schema a blocchi

delle due schede.

Il nucleo centrale di questa implementazione è rappresentato

dallo switch HSR che effettua l’inoltro (forward) dei frame

HSR/Ethernet da porta a porta. Nell’implementazione pre-

sa in considerazione vi sono quattro porte, una delle quali

è collegata al processore ARM di tipo hard, in modo da con-

sentire l’invio e la ricezione di frame Ethernet. Le restanti

porte HSR/Ethernet sono connesse, attraverso blocchi di

adattamento GMII-1000BASE-X e (G)MII-SGMII, ai moduli

SFP e ad altri dispositivi. Un numero di porte esterne pari

a tre è sufficiente per l’implementazione di RedBoxes (box

di ridondanza) dedicati (maggiori informazioni nel riquadro:

I

Tecnologie basate

su Internet

per le smart grid

Come implementare i protocolli di ridondanza HSR e IEEE 1588 PTP con i SoC FPGA di Altera su cui gira il

sistema operativo Linux

Jouni Kujala

Flexibilis Oy

Tampere, Finland

Fig. 1 – Scheda di sviluppo SoC e scheda SFP di Terasic