XXIV

Power

POWER 14 -

SETTEMBRE 2017

un circuito di aggancio o di protezione contro le sovra-

tensioni.

Induttanza del loop:

a causa dell’elevato slew rate e

dell’alta frequenza di commutazione del GaN, qualsiasi

induttanza parassita nel progetto introduce perdite e

oscillazioni nel sistema. In un progetto sono presenti

molte fonti di induttanza, compresi i conduttori e i fili

di collegamento interni (bond wire) sia nei package dei

FET GaN sia dei driver, nonché le piste presenti sulla

scheda a circuito stampato (PCB). Anche se è possibile

ridurle, la loro eliminazione è molto difficile. Le solu-

zioni con lo stadio di potenza in GaN, come ad esem-

pio LMG3410, integrano il driver e i FET GaN in un

unico package, riducendo notevolmente l’induttanza

complessiva.

Ritardo di propagazione:

ritardi di propagazione ri-

dotti e un buon adattamento (per le topologie a semi-

ponte – half-bridge) sono fattori molto importanti per

il funzionamento ad alta frequenza. Un ritardo di pro-

pagazione nell’ordine di 25 ns e una adattamento com-

preso tra 1 e 2 ns sono un ottimo punto di partenza per

progetti ad alta frequenza (operanti 1 MHz o più). Con

l’ottimizzazione del progetto del circuito di pilotaggio

del gate e del layout del PCB, è possibile far funzionare

un dispositivo GaN con slew rate molto alti (>100 V/ns)

e oscillazioni minime sul nodo di commutazione. La

figura 2 mostra un esempio di forma d’onda di commu-

tazione relativa a un progetto di questo tipo.

Esempio di progetto: soluzione PFC di nuova generazione

Grazie alle sue caratteristiche uniche, il GaN consente

ai progettisti di superare alcune delle sfide più difficili

legate all’aumento della densità di potenza in diversi

sistemi e applicazioni.

Questi vantaggi non derivano semplicemente dalla so-

stituzione di un MOSFET con un dispositivo GaN equi-

valente in un progetto esistente.

Il GaN permette di implementare nuove topologie di

circuito e/o modalità operative che non erano possibili

con i MOSFET in silicio.

I vantaggi che è possibile conseguire permettono lo

sviluppo di nuove classi di prodotti che abbinano di-

mensioni inferiori e maggiore efficienza. Un esempio è

riportato di seguito.

La correzione del fattore di potenza (PFC) è indispen-

sabile in ogni prodotto elettrico o elettronico che con-

sumi più di 75W. PFC è il primo blocco di conversio-

ne di potenza che si trova tra la rete e il resto

del sistema e deve supportare l’intero carico in

qualsiasi punto di funzionamento.

Per questa ragione ha un impatto diretto su di-

mensioni ed efficienza dell’intero sistema. Nel

corso degli anni sono state progettate genera-

zioni di differenti topologie con l’obiettivo di

ridurre le dimensioni e soddisfare gli standard

di efficienza in vigore in ambito industriale.

I livelli di efficienza definiti dallo standard 80

Plus, ad esempio, richiedono un’efficienza del

96% per gli alimentatori “titanium grade”.

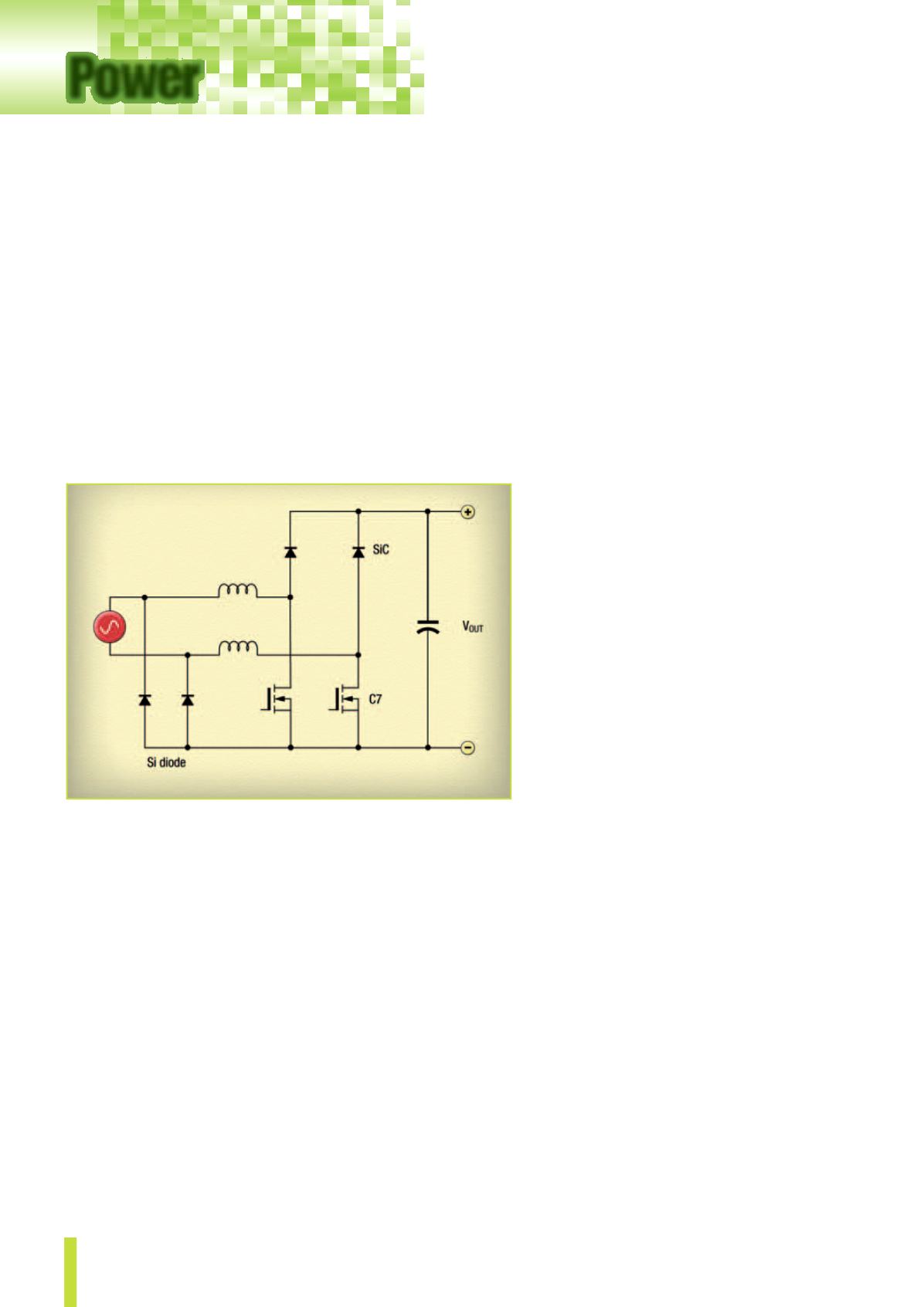

Molti sistemi ad alta potenza (>1 kW) utilizzano

la topologia a doppio ponte (dual-bridge) ripor-

tato in figura 3.

Nell’ultimo decennio, grazie all’introduzione di

diodi al carburo di silicio (SiC) e dei transistor

MOSFET a super-giunzione delle più recenti ge-

nerazioni, è stato possibile ottenere alcuni mi-

glioramenti in termini di densità.

Miglioramenti che tuttavia hanno raggiunto il massimo

delle loro potenzialità in termini di efficienza e densi-

tà di potenza. Un significativo aumento della densità

di potenza richiede un approccio alternativo che sia in

grado di ridurre:

-

menti preposti al raffreddamento.

Un’alternativa è la topologia Totem-Pole a conduzio-

ne continua. Questa topologia sfrutta al meglio tutte le

potenzialità del GaN, rendendo in definitiva possibile

la realizzazione di progetti contraddistinti da dimensio-

ni minori e frequenze operative superiori (Fig. 4). Il

recupero inverso nullo del GaN è un fattore di fonda-

Fig. 3

– La topologia PFC dual-bridge è spesso utilizzata in numerosi progetti ad alta

potenza