EDA/SW/T&M

VERIFICATION IP

58

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

L’

aumento del numero di transistor, della complessità

architetturale e dell’interdipendenza con il software

ha contribuito a rendere molto più impegnativo il pro-

cesso di verifica dei SoC. Il vantaggio di tale evoluzione è le-

gato al fatto che gli investimenti commisurati, nello sviluppo di

soluzioni di verifica avanzate, garantiscono importanti ritorni.

Uno degli aspetti di maggior impatto nel settore è che la veri-

fica dei SoC avanzati non è più un’attività realizzabile con un

unico engine. Per quanto concerne le metodologie di verifica

avanzate, ciò a cui si assisterà sempre più frequentemente è

un approccio olistico basato su un insieme di engine diffe-

renti.

Oggi, la verifica deve essere eseguita in parallelo a tutti i

livelli, partendo dal sistema fino a scendere verso il silicio,

spostandosi verso l’alto o verso il basso a seconda dei casi.

Questo approccio parallelo è ciò che Cadence Design chia-

ma System Enablement (o SDE), concetto che pone l’accen-

to sullo sviluppo di sistemi o prodotti finali completi. In tale

contesto, tutto interagisce con tutto il resto; arrivare a un

design ottimale implica la capacità di gestire questa nuova

realtà, integrando i domini elettrico, software e meccanico

nei processi sia di sviluppo sia di verifica.

Maggiore disponibilità di tecnologie di verifica

con maggiore comunanza

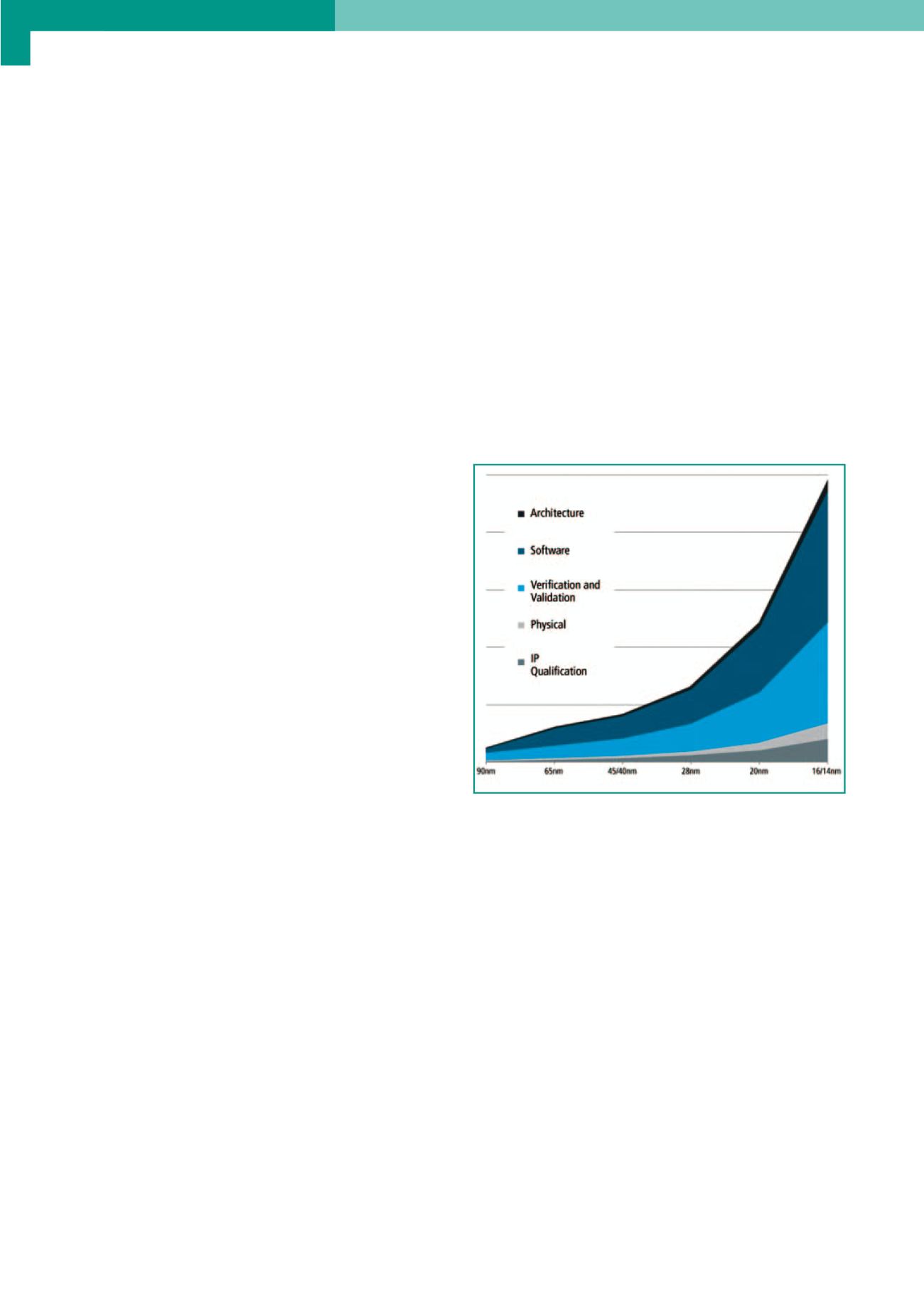

Come illustrato in figura 1, la riduzione delle geometrie di

processo implica un aumento di complessità delle attività

di verifica. Fortunatamente, negli ultimi anni, abbiamo visto

un’enorme evoluzione e uno sviluppo altrettanto significati-

vo delle tecnologie di verifica. Un grande cambiamento ri-

guarda l’omogeneità delle interfacce tecnologiche, che sono

migliorate incommensurabilmente. Ad esempio, solo fino a

10 anni fa, ottenere un design eseguibile in un emulatore

richiedeva letteralmente mesi di lavoro. Oggi, il design può

essere semplicemente compilato. Anche le interfacce utente

per il debug dei progetti presentavano delle significative dif-

ferenze in base a ogni approccio, mentre oggi sono comuni.

Lo stesso vale per gli strumenti per la misura della copertu-

ra; questi tool hanno percorso una lunga strada da quando

richiedevano il tracciamento e la manutenzione di enormi

fogli di calcolo.

Oggi, abbiamo a disposizione un novero più ampio di tecno-

logie di verifica. Queste hanno anche molto di più in comu-

ne tra loro, aspetto che consente di semplificare il processo.

Le tecnologie di verifica principali includono la simulazione,

gli approcci formali, le piattaforme virtuali, l’emulazione, e la

prototipazione FPGA. Benché ogni singola tecnologia abbia

uno scopo preciso, una strategia di verifica completa per un

SoC di grandi dimensioni realizzato a un nodo tecnologico

avanzato implica il ricorso a tutte le soluzioni, come indicato

in figura 2.

Un continuum tra i motori di verifica

Quando si tratta di tecniche, alcuni progetti partono da un

livello molto elevato di astrazione, dove la verifica consiste

nell’eseguire un codice C. Tale approccio è valido, ad esem-

pio, per molti algoritmi di visualizzazione, che possono essere

successivamente compilati utilizzando una sintesi di alto livel-

Verifica SoC:

il punto della situazione

Steve Carlson

Cadence Design Systems

Oggigiorno la verifica SoC richiede un

approccio olistico basato su una piattaforma

di tecnologie