DIGITAL

FPTA

63

- ELETTRONICA OGGI 439 - SETTEMBRE 2014

i transistor si introduce una mutazione genetica ossia una

modifica alle funzioni operative eseguibili dal sistema, con il

valore aggiunto che è il sistema stesso a verificare l’adegua-

tezza delle prestazioni e a decidere di provare nuove confi-

gurazioni operative per migliorare l’efficacia delle funzioni

eseguite.

Transistor cromosomi

In pratica l’array è formato dai transistor che rappresentano

gli elementi logici e da un intreccio di piste di collegamento

fra di essi, le quali contengono

degli ulteriori transistor configu-

rati come interruttori, o switch,

che possono aprirsi o chiudersi,

abilitando o interrompendo i per-

corsi e perciò cambiando il lay-

out del circuito risultante. In altri

termini, una cella logica elemen-

tare è composta da otto o sedici

transistor principali attorniati da

un numero circa doppio di tran-

sistor utilizzati come switch di

comando e il tutto può essere

replicato in array con migliaia

di celle, per ottenere sistemi più

complessi. Il motore di controllo

agisce sulla rete degli interrut-

tori per imprimere le funzionalità

operative alle cellule, in base ai

test di adeguatezza che esegue

continuamente, confrontando

ciò che viene prodotto in uscita

con quanto entrato all’ingresso,

in relazione alle regole che ha

in memoria, che rappresentano gli schemi operativi fonda-

mentali.

Se con queste regole non ottiene un indicatore di adegua-

tezza sufficiente, allora comincia a modificare gli schemi

operativi fondamentali, creando nuove regole in base a dei

criteri preimpostati dal progettista e pensati per lasciare

qualche grado di libertà al motore di calcolo, affinché rie-

sca a generare piccole e casuali modifiche sostanziali sulle

funzionalità circuitali. In pratica, rileva quali transistor di

ogni cella sembrano meno efficienti e fra essi ne sceglie

a caso qualcuno e gli cambia la polarizzazione aprendo o

chiudendo i transistor di comando che gli stanno intorno.

Quindi, esegue di nuovo il test di adeguatezza per verifica-

re se il livello di fitness migliora o peggiora e nel secondo

caso annulla le ultime modifiche effettuate e ne sceglie altre.

Questo ciclo viene ripetuto continuamente su tutte le celle

dell’array o se si vuole su tutti i geni, finché l’indicatore

di fitness non aumenta a un livello accettabile, attestando

l’avvenuta mutazione genetica della matrice di transistor

o che dir si voglia l’evoluzione hardware della logica pro-

grammabile. Questa fase caratterizza l’hardware evolutivo

ed è la più laboriosa da mettere a punto per il progettista,

perché lo costringe a provare su un prototipo un gran

numero di configurazioni fondamentali e verificare le loro

possibili alterazioni e le conseguenti mutazioni genetiche,

implementate dalla cella per valutarne l’adeguatezza e sta-

bilire così i criteri da impostare come ‘leggi genetiche’ di

riferimento, alle quali il motore di calcolo si dovrà ispirare

per decidere come far evolvere la logica programmabile

nel suo ciclo vitale, una volta installata nell’applicazione alla

quale è destinata. Va notata la differenza con la funzione di

riconfigurazione dinamica di cui sono dotati alcuni moderni

Fpga, perché in questo caso la riconfigurazione avviene

semplicemente ricopiando dalla memoria un nuovo layout

preparato dal progettista, allo scopo di aggiornare il dispo-

sitivo e quindi non si può parlare di un’evoluzione auto-

noma vera e propria ma semmai di un ammodernamento

imposto dall’esterno.

Q

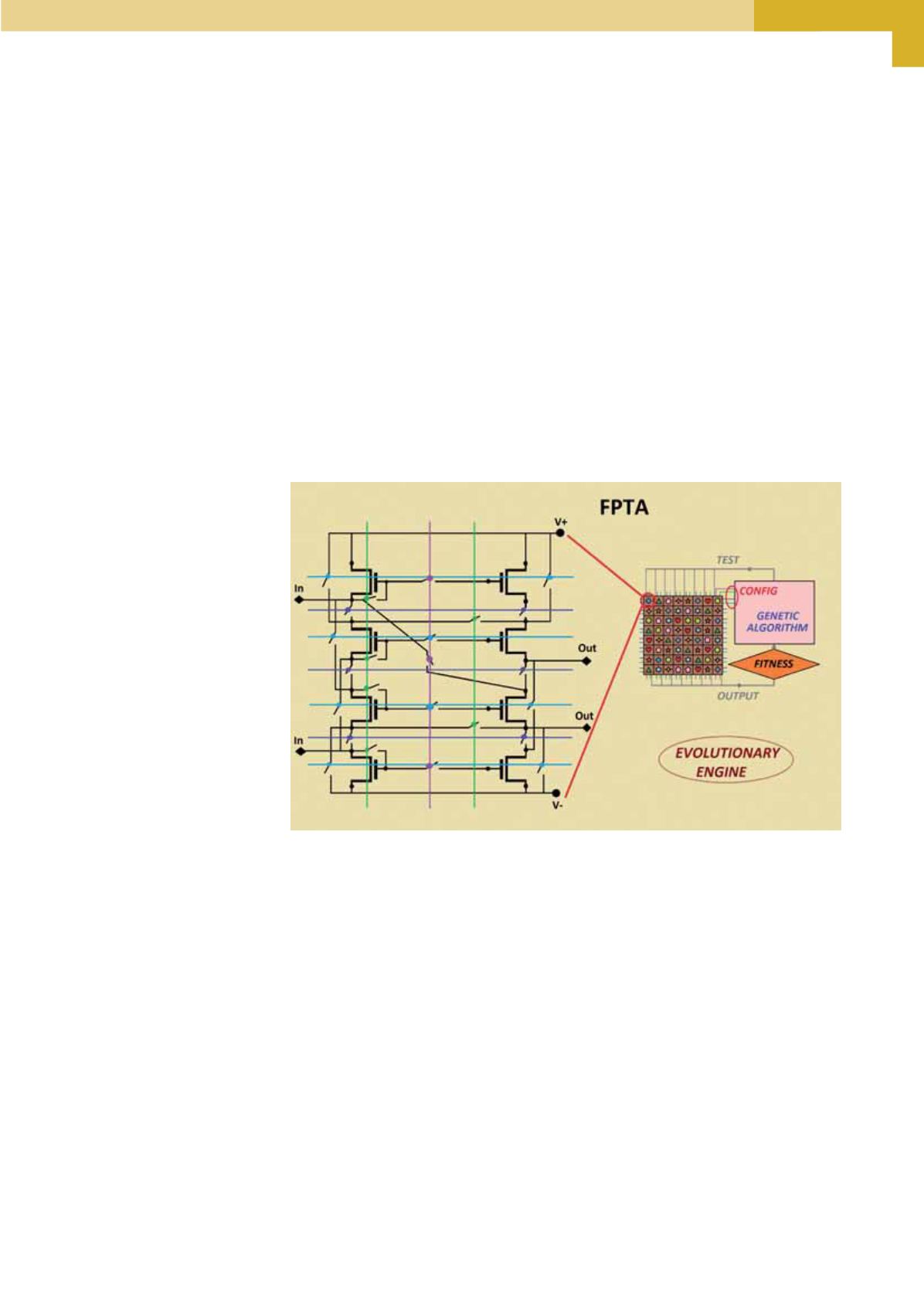

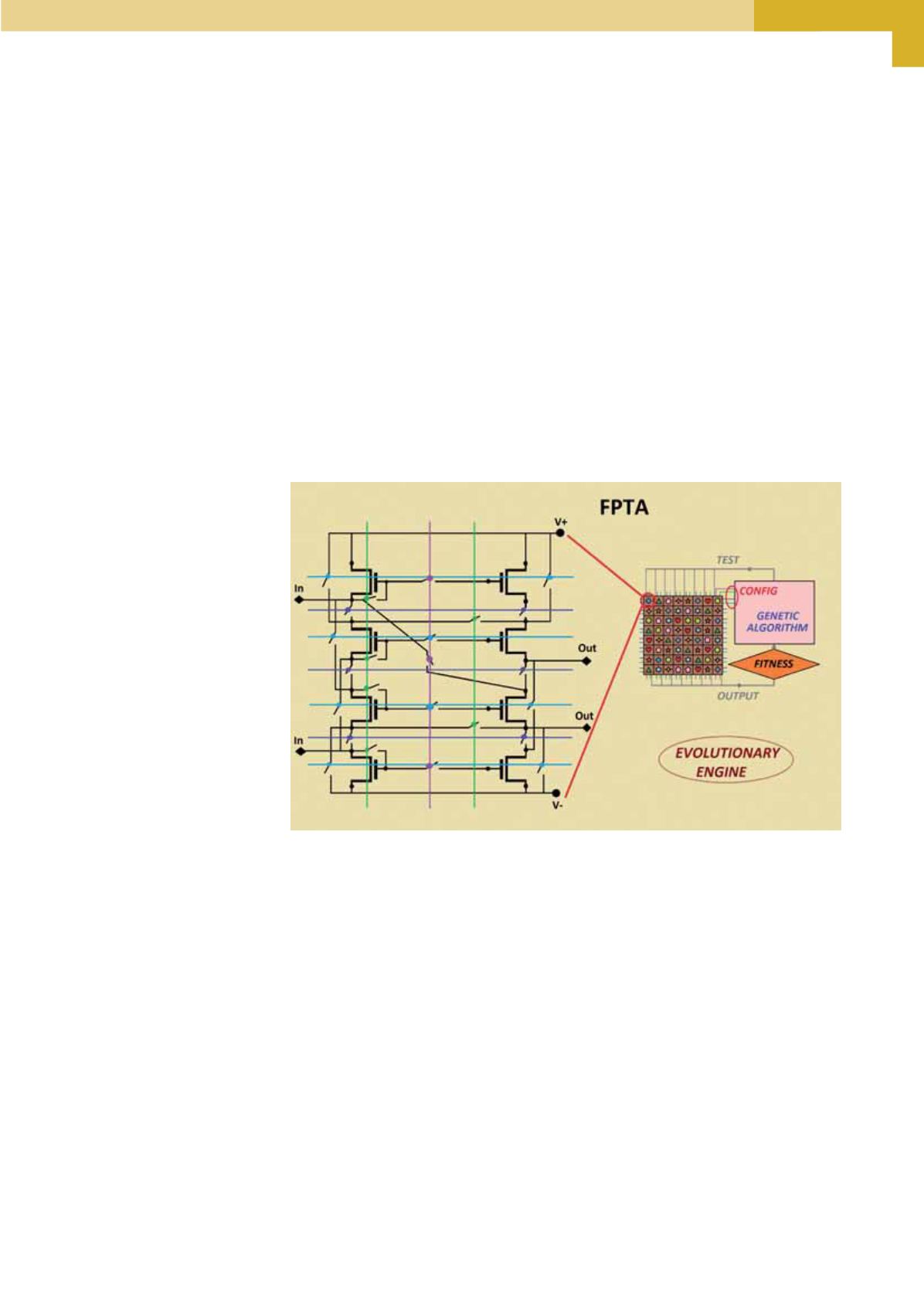

Fig. 1 – Schema di un blocco hardware evolutivo con 8x8 celle logiche FPTA la cui adeguatezza funzionale

è monitorata da un algoritmo genetico che decide come modificare la configurazione dei transistor di

ciascuna di esse per migliorare l’efficacia operativa a livello di sistema