61

- ELETTRONICA OGGI 436 - MAGGIO 2014

DIGITAL

SoC

di Altera. Il dispositivo risulta formato da un sottosistema

(denominato HPS – Hard Processor System) ARM Cortex-

A9 dual core e un FPGA in tecnologia da 28 nm integrati in

un unico chip. I componenti delle architetture hardware e

software sono (Fig. 3) sono sintetizzate di seguito:

Architettura hardware

Due DMA per trasferire i dati dall’i/O dell’FPGA ai proces-

sori ARM e viceversa.

I due DMA sono collegati alla

porta ACP per trasferire i dati

direttamente verso/dalla memo-

ria cache del processore ARM.

IP dell’unità di controllo in

tempo reale per avviare il tra-

sferimento dei messaggi tra i

processori ARM e gli engine

DMA il più rapidamente possi-

bile.

Monitor del jitter per acquisire

le prestazioni in tempo reale e il

jitter mediante il probing diretto

dei segnali DMA, con un’accura-

tezza compresa tra ±6.7 ns.

Architettura software

RTOS VxWorks che gira in

modalità SMP sui processori

ARM dual core.

Isolamento del core utilizzato per l’assegnazione dell’ap-

plicazione real-time al primo core e le restanti applicazioni

– con caratteristiche non real-time – al secondo core.

L’applicazione in real-time preleva in maniera continua

un dato dall’I/O, lo elabora e invia di nuovo i risultati all’I/O.

Le applicazioni di tipo non real time sfruttano al massimo

le caratteristiche del core ARM e degli I/O facendo girare

in modo continuativo trasferimenti FTP e funzioni di deco-

difica dei dati.

Risultati sperimentali

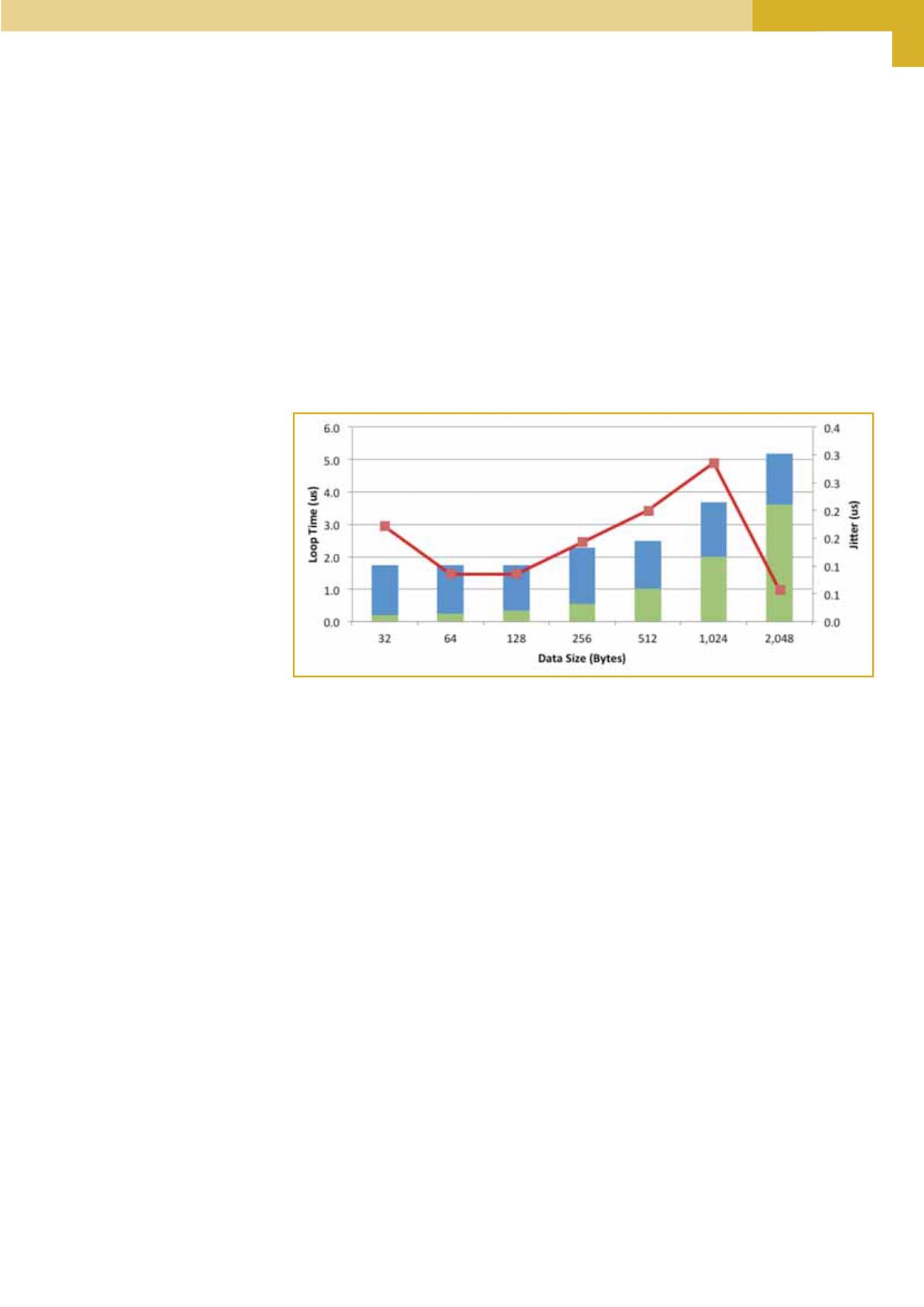

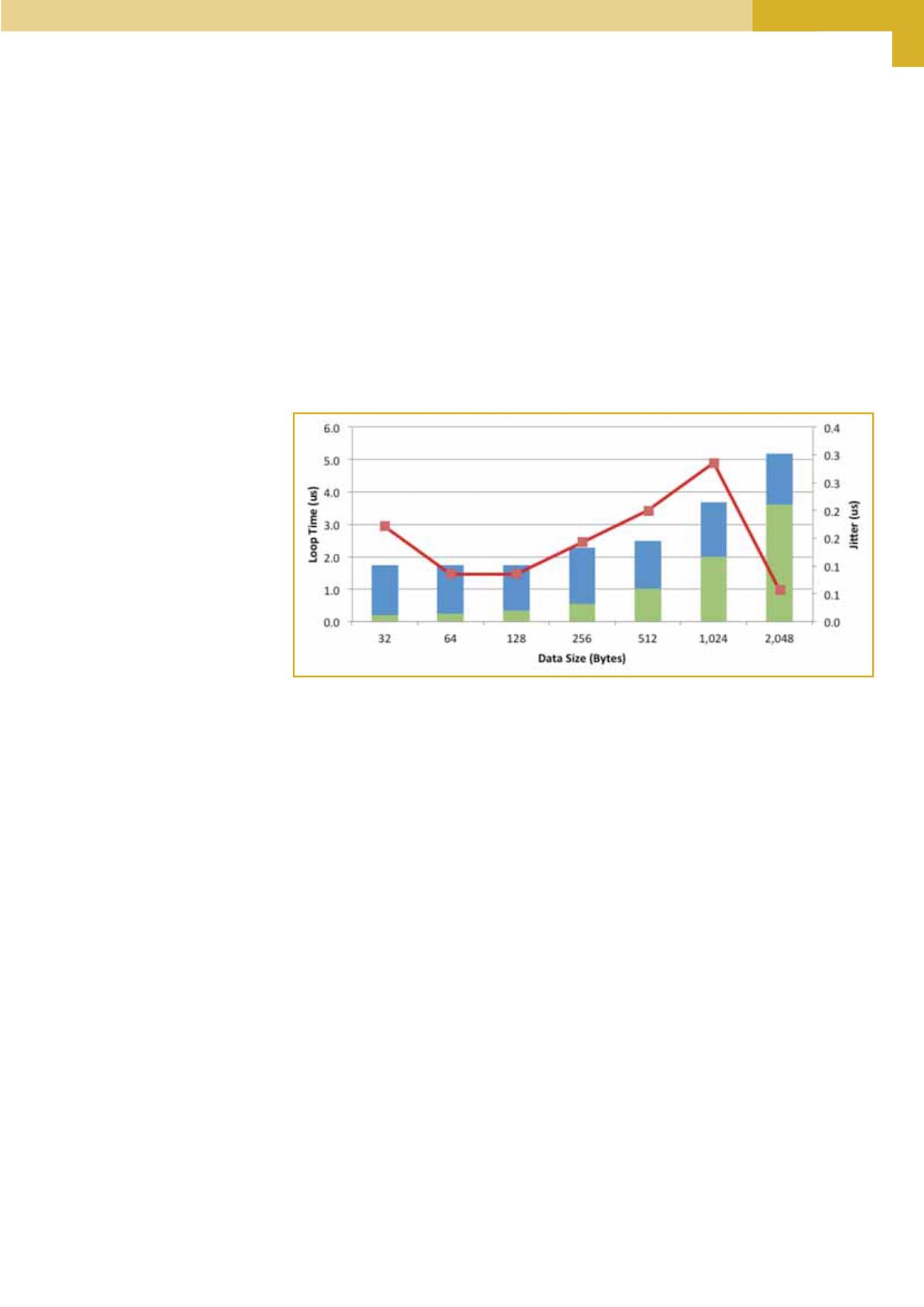

Sono stati condotti esperimenti utilizzando dimensioni di

dati differenti (da 32 byte a 2.048 byte). Questi dati sono

stati fatti girare milioni di volte in modo da poter ottene-

re un istogramma del loop time per l’analisi del jitter (la

differenza tra il loop time massimo e minimo). Come si

può desumere osservando il grafico di figura 4, anche in

presenza di un notevole volume di traffico FTP che gira

sul secondo core, è stato possibile ottenere una latenza

dell’ordine del microsecondo con un jitter inferiore a 300

ps nel corso di milioni di test run (cicli di esecuzioni del

test). A seconda delle dimensioni dei dati si possono osser-

vare alcune oscillazioni del jitter che risultano comunque

contenute entro 200 ps, un valore privo di significato per

questi livelli di throughput.

La medesima applicazione FTP è stata fatta anche girare

sul sistema operativo VxWorks operante in modalità SMP

utilizzando entrambi i core, ottenendo un incremento di

velocità di un fattore molto prossimo a 2. Questa tecnica

non ha dunque conseguenze negative sul throughput e

rappresenta senza dubbio la soluzioni ideale nel caso vi

siano contemporaneamente applicazioni hard real time e

ad elevato throughput. Una soluzione AMP evidenzia una

penalizzazione della medesima entità a causa del parti-

zionamento hard dei core, ma ha lo svantaggio di essere

meno scalabile all’aumentare del numero dei core.

In definitiva, nella progettazione di un sistema SoC in cui

coesistono applicazioni che richiedono un elevato throu-

ghput e applicazioni con requisiti real time è necessario

tener conto dei seguenti fattori:

Trasferimento dei dati in modalità DMA.

Coerenza della cache.

Trasferimento dei messaggi tra il core del processo e

l’engine DMA.

Partizionamento del sistema operativo.

Scalabilità del software all’aumentare del numero dei

core.

In questo articolo è stato dimostrato che un progetto che fa

ricorso a un’elaborazione di tipo SMP con isolamento del

core e un trasferimento che sfrutta la coerenza della cache

permette di ottenere prestazioni in real time con bassi

valori di latenza e jitter, preservando nel contempo la sca-

labilità richiesta per i SoC delle prossime generazioni.

Q

Fig. 4 – Risultati sperimentali ottenuti in termini di jitter e di loop time