POWER 2 - luglio/agosto 2013

XV

MOSFET

bassa tensione. La figura 1 evidenzia il ruolo svolto da un

MOSFET a bassa potenza in due circuiti di conversione

della potenza utilizzati nello stadio di alimentazione di

un tipico sistema di telecomunicazione. In figura 1a, pos-

siamo vedere lo schema a blocchi di un alimentatore AC/

DC in configurazione flyback, che converte la corrente

alternata di rete in una linea di distribuzione in DC a 48

V. In questo caso, i MOSFET ad alta tensione con valore

nominale dell’ordine dei 600 V effettuano la commuta-

zione e la correzione del fattore di potenza (cos φ) sul

primario, mentre un MOSFET a bassa tensione con una

V

DSS

compresa tra 100 V e 200 V offre la commutazione

richiesta al secondario. La figura 1b mostra il convertito-

re isolato DC/DC a ponte intero (full-bridge), nel quale

si utilizzano dei MOSFET a bassa tensione con tensioni

nominali comprese tra 60 V e 250 V per gestire la com-

mutazione sul primario. In questo caso, la commutazione

al secondario è gestita da MOSFET con tensioni nomi-

nali comprese tra 30 e 60 V. Proseguendo ulteriormente,

MOSFET a bassa tensione saranno anche impiegati nelle

commutazioni sul ramo superiore (high-side) e inferiore

(low-side) del ponte dei convertitori nel punto di carico

(Point Of Load, POL) non isolati, utilizzati per fornire

le bassissime tensioni richieste dai processori di sistema

e dalla memoria. In passato, identificare un MOSFET di-

screto sufficientemente efficiente poteva consistere sem-

plicemente nel confrontare le resistenze di conduzione

(R

DS(ON)

) dei diversi dispositivi. Tuttavia, fattori come la

necessità di avere commutazioni sempre più veloci e den-

sità di potenze sempre maggiori indicano che i progettisti

devono oggi considerare diverse “cifre di merito” se desi-

derano sfruttare il MOSFET con le prestazioni migliori.

Sebbene le perdite di conduzione restino sempre un fat-

tore importante e vadano confrontate valutando il pro-

dotto R

DS(ON)

*A (resistenza di conduzione per unità di

superficie), anche le perdite di commutazione causate

dalle induttanze parassite e dalla carica di gate rappre-

sentano un elemento significativo. Per giunta, siccome le

perdite cambiano a seconda del carico, può essere utile

considerare caratteristiche come il prodotto R

DS(ON)

*C

iss

(resistenza di conduzione per capacità di ingresso), una

cifra di merito relativa alle perdite che possono avere un

impatto significativo sui circuiti di alimentazione in pre-

senza di carichi leggeri.

Meno compromessi

Uno dei problemi dei costruttori di MOSFET di poten-

za è il fatto che se una cifra di merito migliora, un’altra

potrebbe peggiorare. L’esempio più ovvio è quando si

riducono le dimensioni fisiche del chip del MOSFET: le

perdite di commutazione migliorano, ma la resistenza di

conduzione peggiora (aumenta). Per questo motivo, i co-

struttori hanno investito risorse significative sviluppando

processi a semiconduttore e tecnologie di incapsulamen-

to finalizzati a limitare questi compromessi indesiderati.

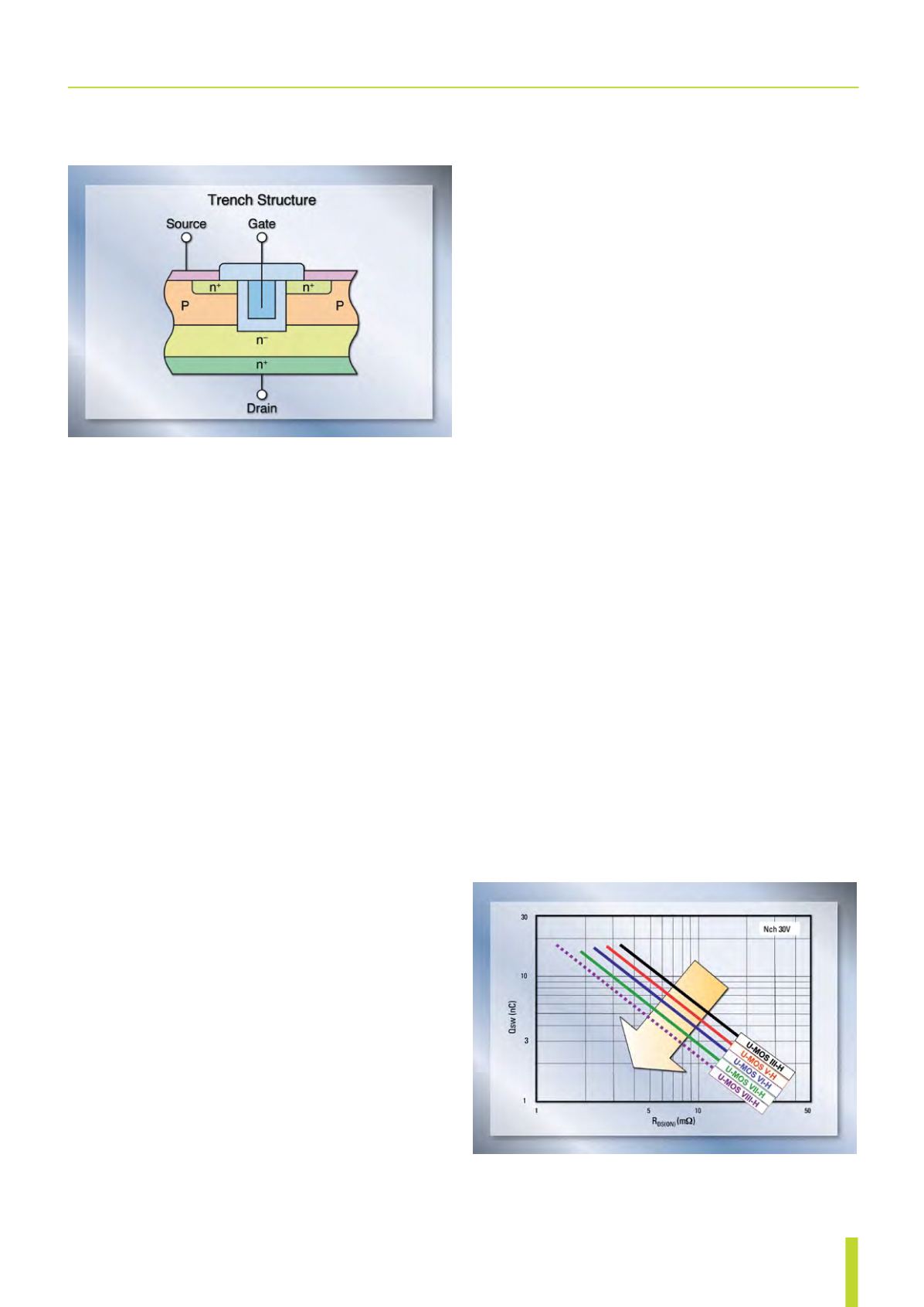

La struttura a trincea illustrata in figura 2 viene attual-

mente utilizzata negli attuali MOSFET con substrato di

semiconduttore, per ridurre in una certa misura la V

DSS

.

Questo processo (che consente di ottenere un’elevata

densità di canale, collegando i canali verticalmente in

modo che formino una scanalatura a U nella regione del

gate) offre una R

DS(ON)

molto più bassa rispetto ad altre

strutture. Il compito dei costruttori, quindi, è stato svilup-

pare e migliorare questo processo in modo da ottenere il

massimo sulle altre cifre di merito.

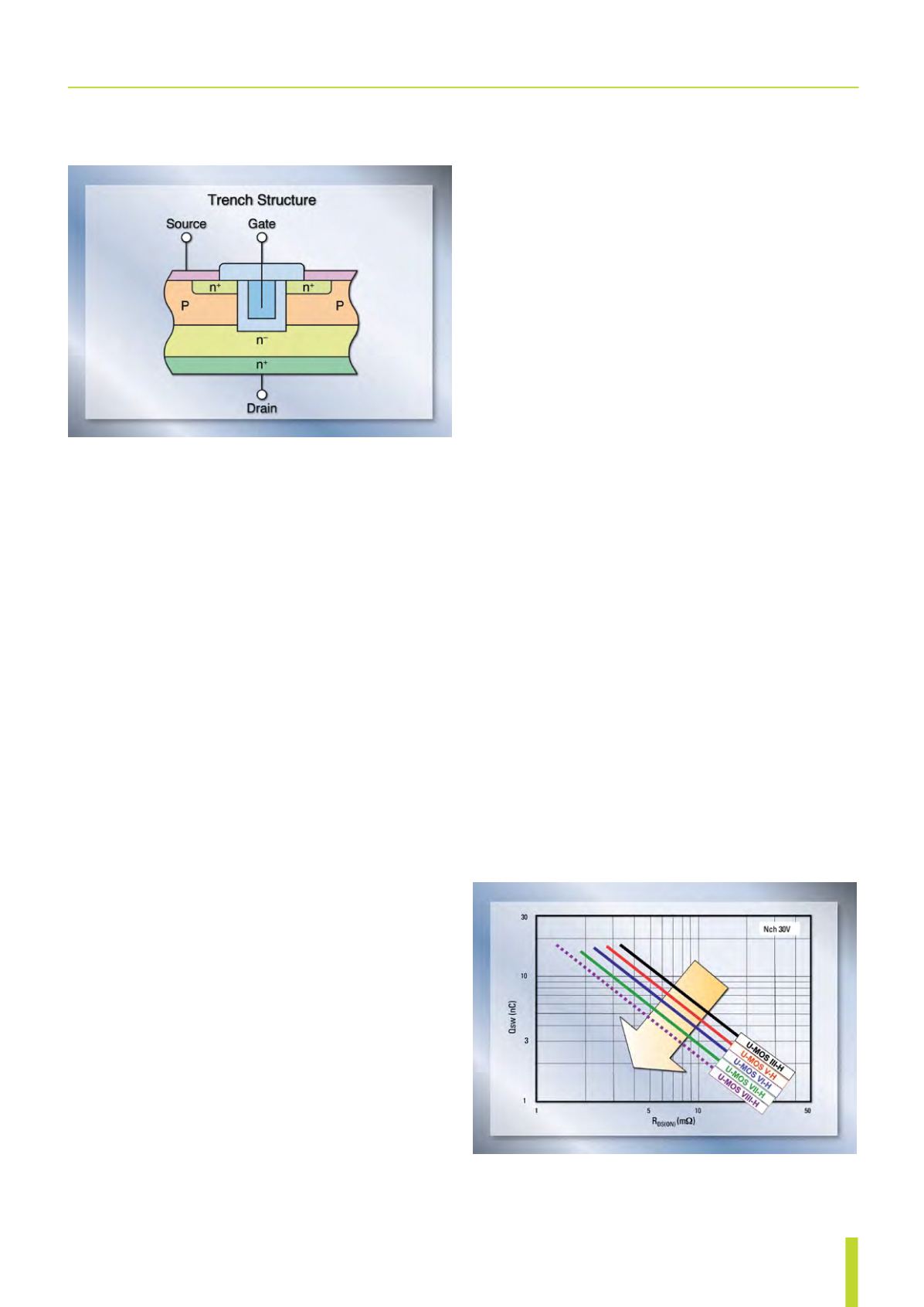

Lo sviluppo più recente di questa tecnologia di processo

a trincea è la struttura U-MOS VIII-H che Toshiba utiliz-

za nella serie di MOSFET LMOS ultra-efficienti e veloci.

Come il nome suggerisce, si tratta dell’ottava generazione

di dispositivi Toshiba U-MOS a trincea in cui l’azienda ha

Fig. 2 - Struttura a trincea per MOSFET a bassa po-

tenza

Fig. 3 - Il trend della commutazione ad alta velocità