POWER 5 - luglio/agosto 2014

XIV

Power

Ogni rete di distribuzione della potenza è un comples-

so intrico di connessioni finalizzato al trasporto della

potenza elettrica dai regolatori di tensione principali

della PCB attraverso la Power Delivery Network (PDN)

fino ad arrivare capillarmente su ciascun transistor e

in questo percorso intervengono svariati contributi di

rumore dovuti alle interazioni a livello di chip, package

e sistema (CPS) che implicano un controllo accurato

sull’integrità della potenza a livello di sistema

Per comprendere appieno la verifica della Power In-

tegrity a livello CPS è fondamentale individuare tutti

i contributi al rumore che i chip, i package e le PCB

(Printed Circuit Board) introducono sulla potenza elet-

trica. A cominciare dal punto terminale della PDN sulla

PCB la potenza è distribuita sull’intera rete di intercon-

nessioni del circuito integrato attraverso una griglia

multi-livello, la quale possiede un’impedenza intrin-

seca che introduce a sua volta un’ulteriore caduta di

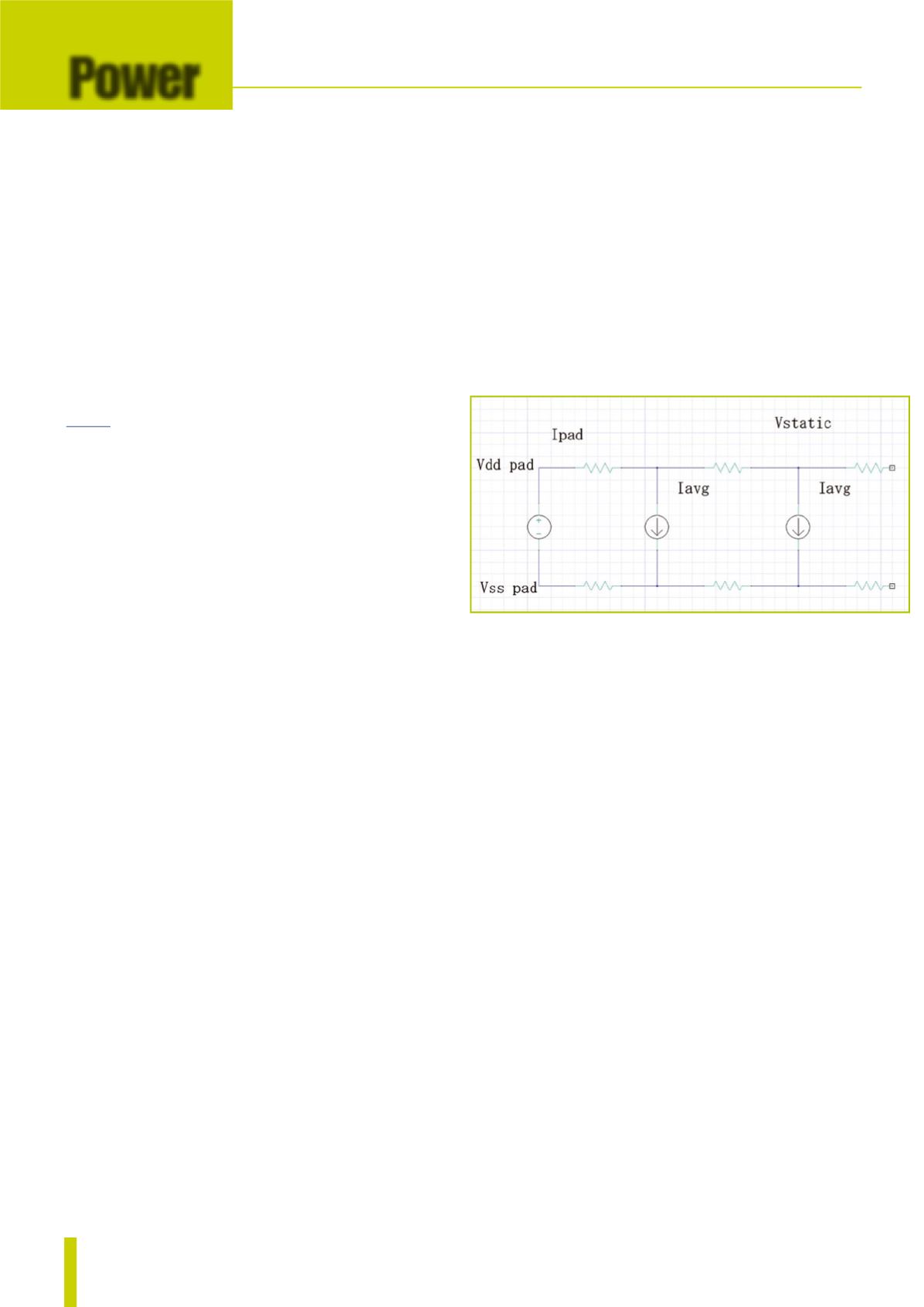

tensione su tutti i transistor. Nel passato l’analisi delle

cadute di tensione ai nodi della PDN veniva spesso fatta

con una ricerca statica delle IR Drop, le cadute (Drop)

di tensione prodotte dal passaggio delle correnti (I) at-

traverso le resistenze (R), secondo la quale i transistor

sono considerati sorgenti di corrente continua media

nel dominio del tempo mentre la rete di distribuzione

della potenza diventa una rete resistiva.

Oggi però l’industria dei semiconduttori ha consentito

alla tecnologia di evolvere ben sotto il micron e alle di-

mensioni nanometriche questo tipo di verifiche hanno

dovuto abbandonare l’analisi statica e preferire le me-

todologie tempo-varianti capaci di rappresentare più

fedelmente il comportamento del chip. Nel dominio

del tempo si considerano infatti tutte le capacità e le

induttanze presenti nella rete di distribuzione della po-

tenza. Gli stessi transistor sono modellati come sorgen-

ti di corrente tempo-varianti che dipendono dall’an-

damento della tensione, del carico e dai transitori di

ingresso istantaneamente presenti in ogni porta logica.

La temporizzazione di ogni cella di un circuito inte-

grato è un fattore critico per analizzarne correttamen-

te l’impatto sulla PDN. Per esempio, ogniqualvolta

un gruppo di transistor commuta simultaneamente si

produce un effetto cumulativo sull’assorbimento di

corrente in quella particolare area circuitale e a ciò si

Sudhir Sharma

High tech industry director

La Power Integrity

come sfida

nella progettazione a livello di sistema

Per Power Integrity si intende la verifica

che serve ad accertare che tutti i transistor

di un circuito integrato abbiano la corretta

polarizzazione per poter garantire il livello

di prestazioni a essi richiesto.

Fig. 1 – Modello per l’analisi statica IR Drop. Un generatore

di tensione continua rappresenta l’alimentazione mentre

i transistor sono considerati come sorgenti di corrente

continua e la rete PDN come una rete resistiva