I vantaggi della tecnologia a 40 nm per la realizzazione dei cruscotti delle auto

L’utilizzo di MCU ad alto grado di integrazione, come i dispositivi della serie Traveo di Cypress Semiconductor, permette ai costruttori di automobili di fascia medio/bassa di realizzare cruscotti nettamente migliori rispetto a quelli tradizionali basati su tecnologie elettro-meccaniche

L’integrazione di display grafici sofisticati nel cruscotto è una tecnica ampiamente collaudata e utilizzata dai costruttori di automobili di fascia alta per differenziare e rendere più attraenti i loro modelli. Audi, ad esempio, ha ottenuto recensioni entusiastiche per il cruscotto ‘Virtual Cockpit’ montato a bordo della 2016 TT roadster (www.cnet.com/roadshow/auto/2016-audi-tt-roadster/#!).

Fig. 1 – Una delle prime realizzazioni di un cruscotto ibrido con grafica 2D montato a bordo della Hyundai Sonata prodotto nel 2012 (Foto cortesia di: Rachel So su licenza di Creative Commons)

Questo nuovo tipo di display per il cruscotto è stimolante dal punto di vista visivo, fornisce informazioni in modo intuitivo, è configurabile “al volo” e in modo semplice per visualizzare differenti tipi di data o immagine in modo pertinente. Dal punto di vista di un utilizzatore comune, questo tipo di cruscotto può essere definito semplicemente “cool” (di tendenza). Il contrasto con i tradizionali quadranti e indicatori elettro-meccanici è senza dubbio impressionante. Grazie alle innovazioni nel campo dell’interfaccia utente di smartphone e tablet, gli acquirenti di automobili sono particolarmente interessati alle prestazioni e all’aspetto dei display all’interno dell’abitacolo. In altre parole, il cruscotto è diventato un importante elemento di differenziazione delle automobile di fascia alta.

Finora, comunque, il cruscotto basato su display grafici sofisticati non ha ancora trovato spazio nel mercato delle nuove auto di fascia medio/bassa. La ragione è molto semplice: i costi elevati. Un display grafico come quello montato a bordo della TT di Audi, che non prevede quadranti e indicatori elettromeccanici richiede un display LCD TFT di ampie dimensioni oltre a un costoso chipset formato da un microcontrollore di fascia alta con un’unità grafica (GPU – Graphics Processor Unit) separata ad alte prestazioni. Il costo della BOM (Bill Of Material) per un sistema di questo tipo è di gran lunga superiore rispetto a quello della BOM di un tradizionale cruscotto elettro-meccanico.

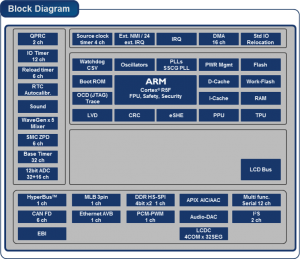

Fig. 2 – Schema a blocchi dei microcontrollori S6J331X/S6J332X/S6J333X/S6J334X della serie Traveo di Cypress Semiconductor

Un costruttore di auto di fascia media in grado di realizzare una versione a prezzi accessibili di un display grafico di fascia alta in un cruscotto potrebbe ottenere un vantaggio competitivo non indifferente. Questo è il motivo per cui gli OEM e i principali fornitori (Tier 1) stanno sviluppando cruscotti di tipo ibrido con display grafici ad alte prestazioni che in pratica abbinano i tradizionali indicatori elettromeccanici su entrambi i lati dello schermo LCD TFT.

Il vantaggio di una configurazione di questo tipo è dato dal fatto che è possibile utilizzare schermi LCD caratterizzati da dimensioni e risoluzioni molto inferiori rispetto a quelle di un display completamente elettronico presente sui veicoli di fascia alta: ciò garantisce una sensibile riduzione dei costi della BOM senza per questo pregiudicare la possibilità di visualizzare informazioni grafiche sofisticate in due o tre dimensioni (2D/3D). Informazioni quali mappe o assistenza al parcheggio possono essere visualizzate in modo molto chiaro in 2D o 3D su un display con una diagonale pari a 3,5”.

L’altro elemento che contribuisce all’elevato costo della BOM di un display completamente grafico è rappresentato dal chipset. Per poter rispettare i severi vincoli in termini di budget tipici dei veicoli di fascia media è necessario ricorrere a una soluzione su chip singolo per l’intero cruscotto. In questo caso la migrazione verso il nodo tecnologico a 40 nm ha rappresentato un’importante evoluzione. Questo nodo tecnologico si è rivelato particolarmente importante per l’industria dei semiconduttori: si tratta di un processo economico, caratterizzato da una resa elevata che permette di integrare più funzionalità (o in alternativa funzionalità migliori) in un chip di dimensioni stabilite.

Il progetto di un cruscotto basato su un chip singolo richiede un livello di integrazione particolarmente spinto: esso può prevedere una CPU ad alte prestazioni, un controllore per LCD, Interfacce di comunicazione operanti ad alta velocità oltre a numerose periferiche. Inoltre, è necessaria una memoria RAM ad alta velocità e di ampie dimensioni, poiché la capacità della memoria vincola la dimensioni e la risoluzione del display che un sistema è in grado di supportare.

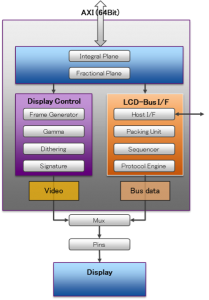

Fig. 3 – Nelle MCU della serie Traveo il controllore del display e il controllore del bus LCD condividono i medesimi pin

L’importanza della memoria

Un esempio delle potenzialità di integrazione offerte dalla migrazione verso il nodo a 40 nm è rappresentata dalla famiglia Traveo di Cypress Semiconductor, formata da microcontrollori (MCU) per applicazioni automotive. Attualmente i dispositivi della linea Traveo sono equipaggiato con un massimo di 4 MB di memoria flash embedded in grado di operare fino a 80 MHz senza cicli di attesa (wait state) unitamente a 384 kB di SRAM. Le nuove MCU S6J331X/S6J332X/S6J333X/S6J334X integrano un core ARM Cortex-R5F che prevede una cache dei dati e delle istruzioni operante a una frequenza massima di 240 MHz e garantisce prestazioni di 400 DMIPS (Fig. 2).

Per molti progetti di cruscotti la dimensione della memoria integrata nei microcontrollori della famiglia S6J33xx è sufficiente, consentendo in tal modo di minimizzare costi, consumi di potenza e ingombri (footprint). Nel caso le risorse di memoria disponibili non fossero adeguate, le MCU della linea Traveo prevedono un’interfaccia HyperBus che può essere utilizzata per il collegamento con una memoria esterna. L’attuale generazione di memorie HyperRAM e HyperFlash di Cypress sono caratterizzate da un’ampiezza di banda di picco di 200MB/s (sull’interfaccia HyperBus a 3V), in modo da consentire il funzionamento a elevata velocità evitando nel contempo l’utilizzo di DRAM, caratterizzate da un costo unitario più alto.

Ancora più importante, l’utilizzo della piattaforma Traveo realizzata in tecnologia da 40 nm consente l’integrazione di tutte le funzioni di un cruscotto ibrido:

- Comunicazione: essa è fornita da un massimo di sei canali che supportano il protocollo di comunicazione CAN-FD (Controller Area Network-Flexible Data). Un MAC (Media Access Controller) Ethernet AVB consente al dispositivo di comunicare con la dorsale delle interconnessioni all’interno del veicolo. Inoltre è disponibile un’interfaccia seriale multi-funzione con un massimo di 12 canali.

- Sicurezza dei segnali e dei dati del cruscotto: questa è garantita dalla funzione SHE (Secure Hardware Extension), una zona sicura all’interno della quale il dispositivo esegue la memorizzazione della chiave, la codifica/decodifica dei dati cifrati utilizzando l’algoritmo AES-128 e la generazione di numeri random.

- Pilotaggio degli elementi elettro-meccanici del cruscotto: la MCU incluse sei controllori per motori passo-passo che sovraintendono al funzionamento degli aghi del tachimetro, del contagiri e così via.

- Sottosistema audio: un mixer audio a 10 ingressi abbinato a un convertitore D/A stereo è un grado di generare un’ampia gamma di suoni sofisticati, che vengono inviati agli altoparlanti del veicolo mediante un’interfaccia I2S a due canali. Cypress mette a disposizione un tool per la creazione dei suoni per supportare questa funzione.

- Controllore LCD: il dispositivo può pilotare un pannello LCD TFT a 4 x 32 segmenti e fornisce una semplice uscita video in formato RGB888.

- Controllo del sistema: il core ARM Cortex-R5F supporta il funzionamento in real time e utilizza il sistema operativo Autosar 4.0.3. Il funzionamento in real time è un elemento cruciale per le funzioni di tipo safety-critical, come il pilotaggio dell’ago del tachimetro.

L’integrazione di tutte queste funzionalità fanno dei dispositivi della serie S6J33xx la soluzione ideale per la realizzazione di cruscotti ibridi dotati di display di piccolo dimensioni: essi infatti permettono ai progettisti di ottimizzare dimensioni e costi della BOM dei loro sistemi e garantire nel contempo una resa (rendering) di ottima qualità della grafica codificata esternamente al chip.

Come visibile in figura 3, le nuove MCU della serie Traveo integrano anche il controllore del bus LCD. Quest’ultimo, unitamente al controllore del display, fornisce un mezzo economico per il pilotaggio diretto dei display. Il piano integrale del sottosistema del display prevede uno strato per il supporto della decompressione. Il piano frazionario può abbinare fino a otto strati con differenti dimensioni, formati dei colori e velocità di aggiornamento. Questi otto strati non possono essere mescolati, ma per entrambi i piani è possibile eseguire l’operazione di alfa blending (controllo della trasparenza degli oggetti). Tutti gli strati possono essere memorizzati in qualsiasi tipo di memoria, comprese memorie HyperFlash o HyperRAM esterne.

Il fatto di poter leggere le informazioni grafiche disponibili da parecchi sorgenti consente di pilotare un display connesso senza ricorrere a un frame buffer, riducendo in tal modo le dimensioni della memoria richiesta per soddisfare le esigenze di display di qualsiasi dimensione o risoluzione.

Grafica avanzata implementata in maniera economica

La migrazione verso il nodo a 40 nm ha permesso a Cypress di incrementare sensibilmente il livello di integrazione – in termini di funzionalità e caratteristiche – delle proprie MCU della serie Traveo destinate ad applicazioni automotive. In particolare, la disponibilità on-board di una flash di capacità massima fino a 4 MB permetterà ai display grafici 2D dei cruscotti ibridi della prossima generazione di funzionare senza ricorrere a memorie esterne, con conseguente drastica riduzione degli ingombri, dei consumi e del costo della BOM del sistema. Questi cruscotti di nuova generazione garantiranno una fruizione da parte degli utilizzatori che può essere assimilabile a quella dei cruscotti completamente programmabili montati a bordo delle auto di fascia alta, a fronte di costi della BOM nettamente inferiori.

L’utilizzo di una soluzione single-chip come le MCU S6J33xx della serie Traveo per la realizzazione di questi nuovi cruscotti ibridi contribuisce anche a semplificare il processo di sviluppo poiché il funzionamento dell’intero cruscotto può essere implementato all’interno di un singolo ambiente di sviluppo che supporta le MCU. Senza dimenticare che grazie alla presenza di altri dispositivi della famiglia Traveo è possibile realizzare cruscotti ibridi di fascia più alta. I componenti la famiglia S6J327Cx, per esempio, integrano engine grafici 2D/3D molto efficienti e supportano alcuni tra i più diffusi tool di sviluppo grafici tra cui CGI Studio e Altia Design.

La disponibilità di un gran numero di versioni della piattaforma Traveo consente ai produttori di modificare in modo semplice il progetto di un cruscotto base per soddisfare le specifiche esigenze dei modelli di fascia più alta o più bassa utilizzando un set singolo di tool di sviluppo.

Con un aumento decisamente contenuto dei costi della BOM i produttori di veicoli di fascia media e di fascia bassa hanno ora l’opportunità di colmare il divario esistente tra i datati cruscotti elettro-meccanici e quelli di tendenza presenti sulle auto di fascia alta.

Note

Ulteriori informazioni sulle MCU della serie Traveo sono reperibili sulla nota applicative AN203898, “Getting started with the Traveo family S6J3300 series MCUs’” disponibile all’indirizzo:

Mathias Bräuer, Director, Product Marketing Cypress Semiconductor

Contenuti correlati

-

Microchip presenta gli MCU a 32 bit PIC32CK con HSM

Microchip Technology ha annunciato la nuova famiglia di microcontroller PIC32CK a 32-bit con sottosistema Hardware Security Module (HSM) integrato e core Arm Cortex M33 con tecnologia TrustZone per isolare e proteggere il dispositivo. L’integrazione di un HSM...

-

Nuovi standard per illuminazione in un’architettura a zone

Microchip mette a disposizione un’ampia gamma di soluzioni, sotto forma di MCU e CIP (Core Independent Peripheral) che permettono di soddisfare le differenti esigenze dei progettisti impegnati nello sviluppo delle soluzioni di illuminazione destinate ai veicoli della...

-

Microchip facilita l’integrazione USB nei sistemi embedded

Microchip Technology ha presentato la famiglia di microcontroller AVR DU con funzionalità USB (come comunicazione dati, alimentazione e aggiornamenti in-field) per i sistemi embedded. Questa nuova generazione di MCU è stata progettata infatti per fornire anche funzionalità...

-

MCU per automotive: Infineon conquista la vetta

Secondo i dati forniti da TechInsights, il mercato globale dei semiconduttori per automotive nel 2023 è cresciuto in misura pari al 16,5%, facendo registrare un fatturato pari a 69,2 miliardi di dollari. Infineon e NXP continuano a...

-

I primi MCU RISC-V sviluppati internamente da Renesas

Renesas Electronics ha annunciato i primi microcontrollori general purpose basati su RISC-V a 32 bit costruiti intorno ad un core sviluppato interamente al proprio interno. Il nuovo gruppo di MCU è siglato R9A02G021 ed è progettato per...

-

Renesas Electronics: MCU serie RA8 per applicazioni di controllo motore

Renesas Electronics ha presentato oggi il gruppo di microcontrollori RA8T1 che consentono il controllo in tempo reale di motori, alimentatori e altri prodotti. Questi dispositivi, basati sul processore Arm Cortex-M85 e la tecnologia Helium, integrano funzionalità PWM...

-

I nuovi MCU di Microchip Technology

Microchip Technology ha rilasciato la sua famiglia di microcontroller PIC16F13145. Questi MCU sono dotati di un modulo Core Independent Peripheral (CIP) e di un modulo Configurable Logic Block (CLB) e consentono la creazione di funzioni logiche combinatorie...

-

Renesas Electronics presenta i microcontrollori del gruppo RA8D1 basati su Arm Cortex-M85

RA8D1 è il nuovo gruppo di microcontrollori (MCU) realizzato da Renesas Electronics ed è il secondo della serie RA8. Si tratta dei primi microcontrollori basati sul processore Arm Cortex-M85 e sono caratterizzati da prestazioni particolarmente elevate, oltre...

-

STMicroelectronics presenta un microcontroller wireless a lungo raggio

STMicroelectronics ha realizzato un nuovo microcontrollore (MCU) wireless caratterizzato da funzionalità di risparmio energetico che consentono di estendere la durata della batteria oltre i 15 anni. Gli MCU wireless STM32WL3 possono essere particolarmente utili per applicazioni come...

-

Core RISC-V per i nuovi microcontrollori a 32-bit di Renesas Electronics

Renesas Electronics ha annunciato di aver progettato e testato una nuova CPU a 32-bit basata sull’architettura open-standard RISC-V. Le nuove CPU RISC-V saranno di complemento alla gamma di microcontrollori (MCU) a 32-bit di Renesas, tra cui la...