Versione HTML di base

EON

EWS

n.

554

-

GIUGNO

2012

16

A

TTUALIT

À

gnerizzazione richiesti per

la manutenzione di ambien-

ti di accelerazione, verifica

e validazione Ice (In-circuit

emulation) separati. Un mo-

tore che però, al contempo,

aggiunge Cadence, consen-

te di mantenere i benefici

degli ambienti tradizionali di

emulazione in-circuit, com-

binandoli con le funzionalità

di analisi evolute disponibili

nella simulazione Rtl.

Nel la fase di val idazione

system-level, la nuova acce-

lerazione in-circuit consente

ai team di lavoro di realiz-

zare un ambiente di verifi-

ca comune e unificato, che

si traduce in un incremen-

to dell’efficienza fino a die-

ci volte. Ottenendo un buon

mix di prestazioni, accura-

tezza e sfruttamento degli

asset Ip esistenti, il sistema

permette di comprimere ul-

teriormente i tempi di svilup-

po dei sistemi e SoC. Un al-

tro aspetto riguarda l’espan-

sione del Verification Ip (Vip)

Catalog, con funzionalità per

l’accelerazione e l’emula-

zione, ancora una volta con

l’intento di spingere i proget-

tisti oltre la classica simu-

lazione Rtl, e velocizzare la

verifica di SoC, sottosistemi

e sistemi. Ora il Vip catalog

include l’accelerazione della

verifica per diversi standard

d’interfaccia (Amba Axi 3/4

e Ace; Pci Express 2.0/3.0;

Usb 3.0; 10Gb Ethernet; Sa-

ta 3; Hdmi 1.4).

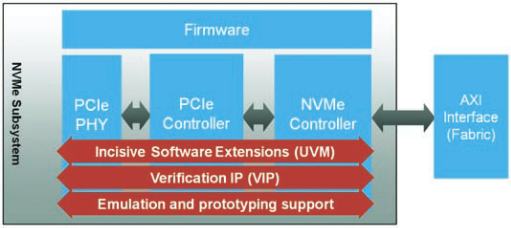

Sottosistema Ip

completo per

il mercato Ssd

Cadence introduce anche

una soluzione che defini-

sce il primo sottosistema Ip,

nel settore dello sviluppo di

soluzioni SoC, in grado di

supportare lo standard NVM

Express 1.0c (non-volatile

memory - NVMe), una tec-

nologia d’interfaccia usata

nel mercato dei drive a sta-

to solido (Ssd – solid state

drive), attualmente in rapida

crescita.

La soluzione comprende

componenti Ip completi: il

controller NVM Express, il

firmware, e i corrispondenti

modelli NVMe e PCIe del

Cadence Verification Ip Ca-

talog. L’elevato livello d’inte-

grazione, afferma l’azienda,

permette di realizzare un’a-

gevole implementazione di

P

iù i tablet e gli smartpho-

ne si di ffondono a r i tmo

esponenziale, più nel mon-

do dei semiconduttori au-

menta il ricorso ai sistemi

SoC (Sys tem-on-Ch i p) .

Fra l’altro, specie nella re-

alizzazione dei prodotti di

elettronica di consumo con

funzionalità wireless e alto

contenuto di componenti Rf,

i processi di progettazione,

integrazione e verifica dei

sistemi e SoC incontrano

una sempre maggiore pre-

senza di circuiti a segnale

misto, diventando sempre

più complessi. Ciò deter-

mina un impatto crescente

sui costi dei progetti e sul

time-to-market dei prodot-

ti finali. A questi problemi

Cadence Design Systems

pon-

de attraverso l’introduzione

di alcune nuove soluzioni,

lanciate ufficialmente a Mo-

naco, in occasione dell’ulti-

della società è espandere

l’offerta, fornendo nuovi mo-

delli di utilizzo per la verifica

dei sistemi e SoC, e nuo-

ve funzionalità e tecnologie

per completare i progetti.

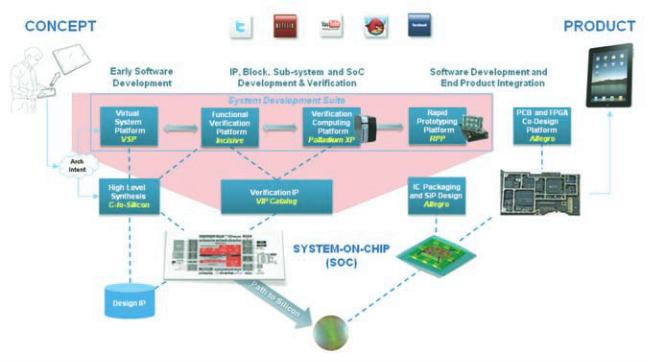

Un fatto importante è l’ag-

giunta nella System Deve-

lopment Suite (Sds) 2012

di una tecnologia di accele-

razione in-circuit, finalizzata

a colmare le inefficienze e

limitazioni prestazionali de-

rivanti dall’utilizzo di piatta-

forme di sviluppo scollegate,

e dalla necessità di manu-

tenzione di diversi ambienti

e motori di verifica (virtual

prototyping, simulazione Rtl,

accelerazione, emulazione,

prototipazione Fpga-based,

e così via), che fa lievitare i

costi e richiede tempo.

In sostanza, Cadence for-

nisce, come parte della su-

ite Sds, un solo ambiente

eterogeneo per la verifica

system- level , scalabi le,

personalizzabile e fonda-

to sulle piattaforme Incisi-

ve e Palladium XP. Insom-

ma, un singolo motore, che

permette ai team di verifica

di evitare gli sforzi di inge-

System-on-Chip,

più strumenti per realizzarli

Cadence Design Systems

amplia ancora l’offerta di tool

per velocizzare la progettazione

dei SoC complessi

G

IORGIO

F

USARI

Fig. 3 - Il

sottosistema

NVMe

Fig. 1 - La suite

di prodotti di

Cadence per

la verifica dei

progetti SoC

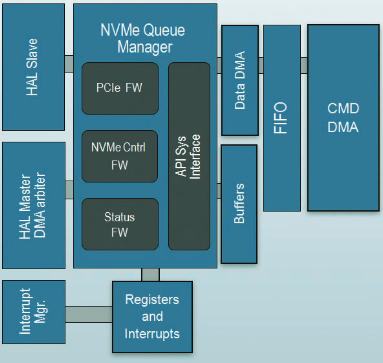

Fig. 2

L’architettura

di NVMe