Basic HTML Version

EON

EWS

n.

549

-

GENNAIO

2012

utilizzati per il tape out di pro-

dotti realizzati con tecnologie

da 28 e 32 nm. Questi circuiti

ASIC per applicazioni mainstre-

am possono essere formati da

alcuni milioni di gate realizzati

con processi da 0,13 o 0,18 mm

che operano a frequenze dell’or-

dine di alcune centinaia di me-

gahertz.

Progetti di questo tipo possono

essere sviluppati senza proble-

mi utilizzando i tool proposti

da Tanner EDA e Incentia che

mettono a disposizione tutte le

funzionalità richieste dai pro-

gettisti che realizzano prodotti

sfruttando tecnologie mature.

Un aspetto che va acquisendo

un’importanza sempre maggiore

nel settore della progettazione

di circuiti ASIC è il costo totale

di possesso (TCO) dei tool EDA.

I maggiori produttori di questi

tool sono legati a un modello di

vendita di licenze vincolate al

tempo.

Il costo per i tool delle più im-

portanti società di questo settore

può essere valutato in 150.000

dollari all’anno e, nell’arco tem-

porale di tre anni in funzione

delle condizioni del mercato,

potrebbe essere dell’ordine di

Nel mondo industriale esiste da lungo tempo la radicata convinzione che per il

progetto di circuiti ASIC – nel dominio digitale, analogico o a segnali misti – i soli

tool in grado di fornire una soluzione adeguata siano quelli forniti dai maggiori

protagonisti del mondo EDA

Una valida alternativa

alla

progettazione di ASIC a segnali misti

L’

ipotesi su cui si fonda tale

supposizione è che i tool per la

progettazione di circuiti integra-

ti a basso costo non forniscano

le funzionalità richieste oppu-

re non dispongano del suppor-

to necessario in termini di PDK

(Process Design Kit – ovvero i

kit di progetto ottimizzati per

una specifica tecnologia di pro-

duzione dei semiconduttori) per

le fonderie di riferimento. Certa-

mente è lecito sostenere che per

un produttore di chip all’avan-

guardia che progetta processori

SoC (System-On-Chip) o control-

lori grafici sfruttando tecnologie

di processo da 28 nm, potrebbe

rendersi necessario un flusso di

progetto del costo di parecchi

milioni di dollari per garantire

prestazioni e puntare a consumi

estremamente bassi.

Nello stesso tempo appare reali-

stica ed economica la proposta

di utilizzare tool che abbinino

un gran numero di funzionalità

a prezzi relativamente contenuti,

per la progettazione di quelli che

vengono comunemente definiti

“mainstream ASIC” (ovvero ASIC

utilizzati in applicazioni di larga

diffusione e quindi caratterizzati

da alti volumi).

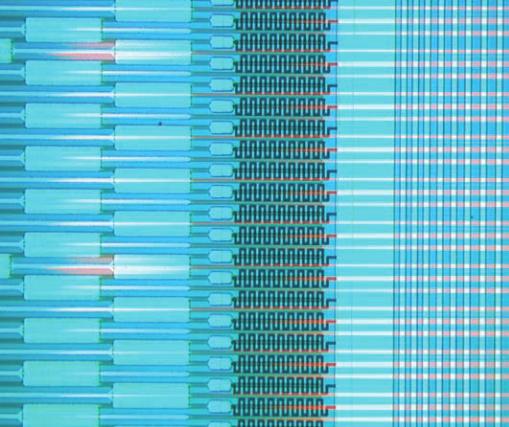

In effetti è disponibile una va-

sta gamma di tool EDA, espli-

citamente ideati per il progetto

di ASIC a segnali misti che ga-

rantiscono livelli di funzionalità

e prestazioni confrontabili con

quelli di analoghi tool di fascia

alta a prezzi nettamente inferiori

rispetto a questi ultimi. In gra-

do di accedere ai PDK delle fon-

derie, questi tool assicurano un

mix ottimale tra produttività ed

economicità.

Il mercato per i circuiti ASIC

analogici e segnali misti rea-

lizzati mediante tecnologie di

processo mature è decisamente

vasto. Le maggiori fonderie ubi-

cate in Europa e in altre parti

del mondo, che non devono ne-

cessariamente fornire tecnologie

di processo allo stato dell’arte,

producono svariate migliaia di

differenti circuiti ASIC in volu-

mi pari a centinaia di migliaia

(se non addirittura di milioni) di

unità ogni anno.

Le società che utilizzando ta-

li fonderie, dal canto loro, non

richiedono necessariamente la

disponibilità di tool di progetto

ideati per superare le problema-

tiche legate ai processi da 32 o

28 nm (o anche inferiori).

Tra le aziende che hanno svilup-

pato tool di prim’ordine per la

progettazione di ASIC mainstre-

am si possono segnalare Tanner

EDA

), specia-

lizzata nel settore della progetta-

zione analogica e a segnali misti

che offre soluzioni corredate da

numerose funzionalità come ad

esempio quelle di piazzamento

e sbroglio (place & route) ol-

tre ad Aldec

e Incentia (

),

specializzate nei tool per la pro-

gettazione digitale corredati da

funzionalità avanzate per quel

che riguarda la sintesi e la simu-

lazione digitale. A questo punto

vale la pena sottolineare il fatto

che i tool di Incentia sono stati

P

AUL

D

OUBLE

PAUL DOUBLE,

managing director

di EDA Solutions

Un aspetto che

va acquisendo

un’importanza

sempre maggiore

nel settore della

progettazione di

circuiti ASIC è il

costo totale del

possesso (TCO)

dei tool EDA

200.000 o 250.000 dollari. Ovvia-

mente potrebbe anche risultare

inferiore, ma si tratta di un ele-

mento non prevedibile.

Da qui il rinnovato interesse

per le licenze perpetue. A parte

il costo iniziale di una licenza

perpetua di un tool di Tanner

o Incentia, per esempio, il solo

costo da sostenere sarà la quota

di manutenzione annuale che

permette di accedere ai servizi

di supporto, agli aggiornamenti

software, alla correzione degli

errori, ai PDK e ai tool dotati di

nuove funzionalità.

Il costo di manutenzione è una

frazione del costo della licenza

originale, ragion per cui i pro-

gettisti possono stanziare un

budget per un periodo molto

lungo. La sicurezza della dispo-

nibilità del prodotto è un altro

elemento da tenere in conside-

razione.

Per esempio, se dopo cinque an-

ni dall’inizio della produzione si

rende necessario un re-spin del

progetto, si ha la certezza della

disponibilità dei medesimi tool

senza incorrere in costi aggiun-

tivi. Il fattore da tenere in con-

siderazione è che esiste un’alter-

nativa al modello di licenza tem-

porale, che permette agli utenti

di scegliere quello più adatto a

soddisfare le loro esigenze sia

progettuali sia di budget.

In definitiva, EDA Solutions met-

te a disposizione una reale alter-

nativa per il progetto di ASIC,

grazie a un flusso di progetto

che abbina elevata produttivi-

tà a costi ridotti, oltre a offrire

tool di tipo puntuale a elevate

prestazioni per la community di

progettisti che si occupano dello

sviluppo di design a segnali misti

per applicazioni mainstream.