57

ACQUISIZIONE DATI |

hardware

EMBEDDED

57 • SETTEMBRE • 2015

golo modulo con le FPGA di controllo di tutti i

moduli adiacenti.

Grazie a una FPGA integrata sulla scheda, è

possibile realizzare un sistema di elaborazio-

ne dei dati real-time dedicato che minimizza il

volume di dati da scambiare e che velocizza i

tempi di elaborazione.

Per rispondere alle specifiche esigenze di

elaborazione richieste dal cliente, compren-

denti sia la conversione di frequenza digitale

che il controllo elettronico della direzione di

propagazione tramite tecniche di beamfor-

ming, il firmware dedicato della FPGA è stato

sviluppato utilizzando il kit di sviluppo per

FPGA U5340A Fdi Keysight.

Le funzionalità del sistema fanno affidamen-

to sia sulla capacità

di elaborazione in

tempo reale offerta

dalla FPGA inte-

grata sulla scheda,

sia della scalabi-

lità

multischeda

resa possibile dalla

presenza dei col-

legamenti punto-

punto tra FPGA

offerti dalle schede

M9703A. Grazie a

questa scalabilità,

la configurazione

da 64 canali potreb-

be essere potenzial-

mente espansa fino

a 104 canali, sem-

plicemente aumen-

tando il numero

di moduli M9703A

inseriti nel cestello

AXIe.

Una soluzione resa

possibile dalla piat-

taforma AXIe

La realizzazione del

sistema di acquisi-

zione dati da 64 ca-

nali di Kesyight per

molti versi è stata

resa possibile dalle

caratteristiche uni-

che della piattaforma modulare AXIe. I pro-

dotti AXIe, e in particolare il modulo M9703A,

costituiscono un’infrastruttura ideale per re-

alizzare un’applicazione per il beamforming

tramite più moduli AXIe.

Ciò è stato ottenuto sfruttando la capacità di

trasferimento dati punto-punto tipica del bus

locale AXIe. L’interfaccia di temporizzazione e

il bus di trigger pervisti nell’architettura AXIe

costituiscono l’infrastruttura di sincronizza-

zione, che permette di condividere il segnale di

clock di riferimento AXIe CLK100 e il segna-

le di sincronizzazione AXIe SYNC a ciascuna

delle schede M9703A.

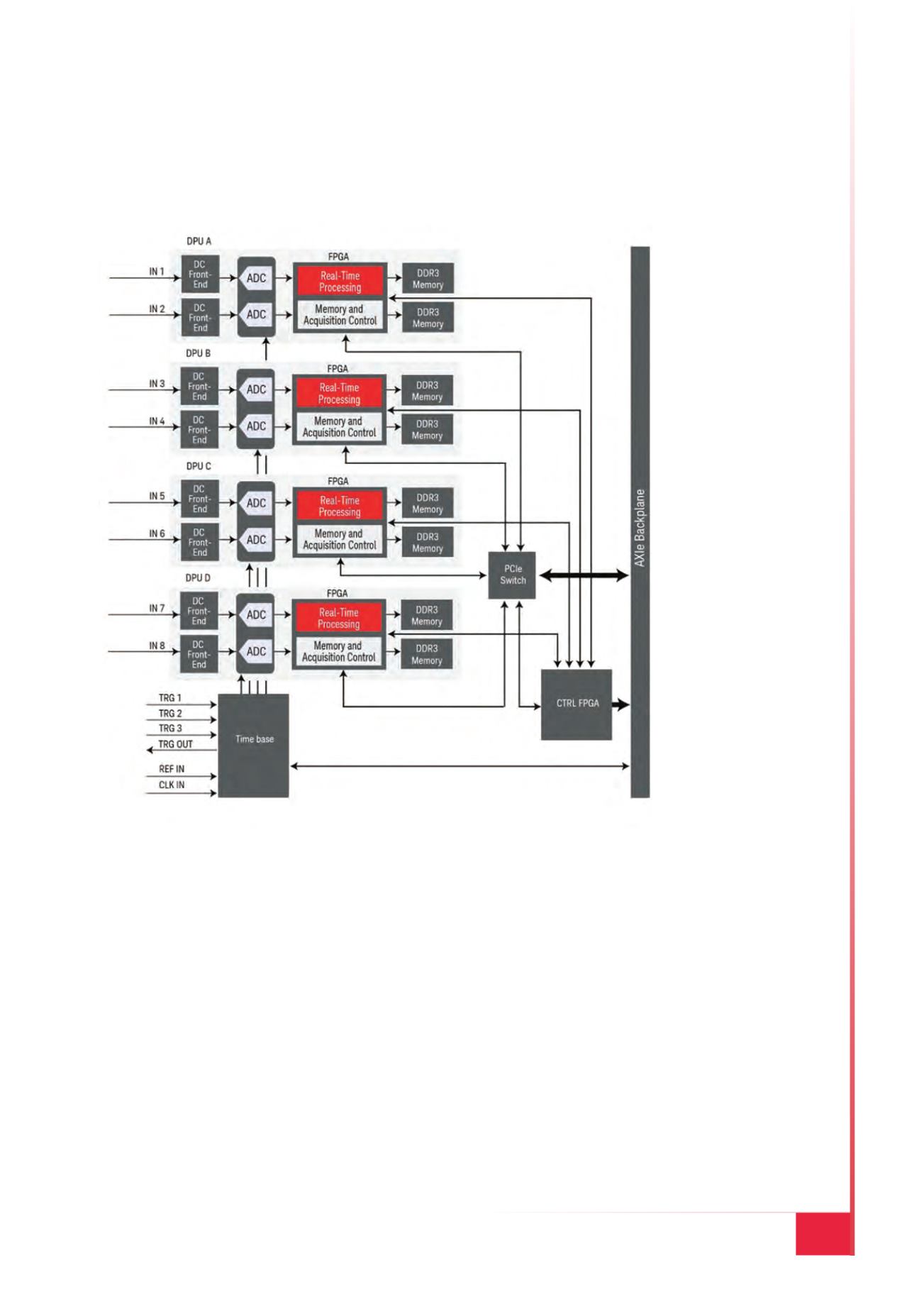

Inoltre, grazie alla molteplicità dei cestelli

Fig. 2 – Schema a blocchi semplificato del digitalizzatore AXIe M9703A