## Gli ADC ad alta velocità per i ricevitori per telecomunicazioni adottano l'interfaccia seriale LVDS

Matthias Feulner

Business Development manager

Wireless Infrastructure

Texas Instruments

*Un esempio di questa nuova generazione di ADC multicanale con interfaccia seriale LVDS è l'ADS6425 di Texas Instruments, un convertitore analogico-digitale a 12 bit e 4 canali con una frequenza di campionamento massima di 125 MSPS*

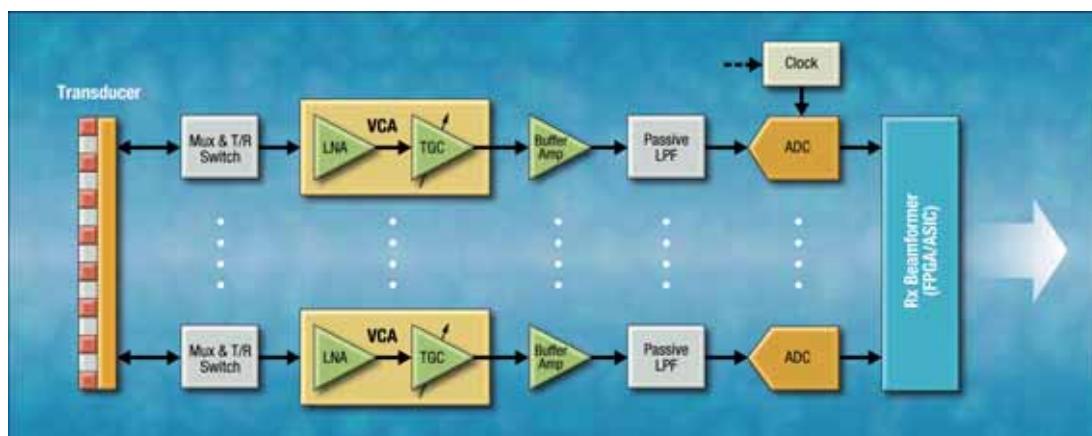

**I**l concetto di serializzazione dei dati in uscita dei convertitori analogico-digitale (ADC) ad alta velocità viene applicato da almeno 4 o 5 anni. I dispositivi di prima generazione dotati di interfaccia seriale LVDS (Low Voltage Differential Signaling) venivano utilizzati principalmente in applicazioni ad alta densità come l'imaging medicale, ad esempio in scanner a ultrasuoni con un massimo di 256 canali per ogni apparecchio. Di norma, tali applicazioni richiedevano basse frequenze di campionamento (tra i 40 e i 65 MSPS) e risoluzioni limitate (tra i 10 e i 12 bit) degli ADC nelle configurazioni con campionamento in banda base. In tal modo era possibile utilizzare fino a 8 canali in un singolo package mantenendo la potenza per canale intorno ai 100 mW [1]. Allo stesso tempo, gli ADC destinati ai ricevitori per telecomunicazioni non

seguirono questo approccio per due ragioni fondamentali:

- I valori di risoluzione e di frequenza di campionamento generalmente maggiori nonché la necessità di supportare il campionamento delle frequenze intermedie (IF) comportavano elevati consumi di energia (nei primi dispositivi spesso > 1 W), per cui non era possibile integrare canali multipli in un singolo dispositivo.

- Maggiori risoluzioni e frequenze di campionamento portavano anche a maggiori velocità di trasferimento dati per l'implementazione in un'interfaccia seria-

**Fig. 1 - Catena del segnale del ricevitore di uno scanner a ultrasuoni per uso medico**

le. Un ulteriore limite era posto dalla tecnologia delle interfacce seriali, in particolare la velocità di trasmissione dati massima raggiungibile e il margine di timing del dispositivo ricevente.

La recente introduzione di nuove architetture di ricevitori per la comunicazione wireless ha avuto come conseguenza una maggiore densità di canali anche in questo campo. Ciò è dovuto essenzialmente a due motivi:

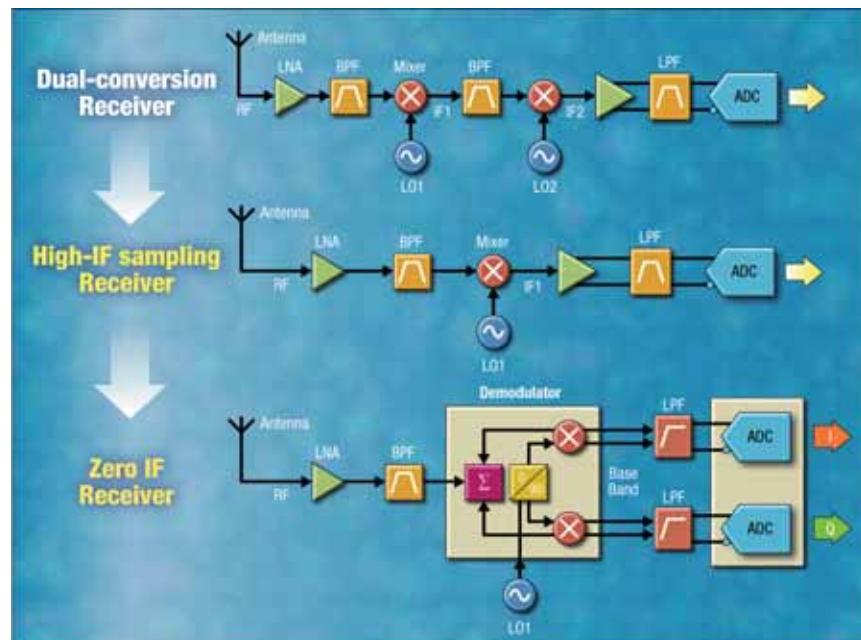

- Ricevitori a conversione diretta, conosciuti anche come ricevitori zero IF. A livello storico, le prime architetture di ricevitori per comunicazioni wireless erano basate sulla doppia conversione, in cui la frequenza del segnale veniva convertita dapprima dalla frequenza radio RF (nella banda di 1-2 GHz) a una frequenza intermedia di poche centinaia di MHz e poi in una seconda frequenza intermedia di alcune decine di MHz, dove il segnale veniva poi campionato dall'ADC. A causa dell'elevata complessità e dei numerosi componenti richiesti, i ricevitori a doppia conversione erano costosi e vennero quindi sostituiti dai ricevitori con campionamento a frequenza intermedia (IF) di seconda generazione, che grazie alle migliori capacità di campionamento degli ADC con frequenze d'ingresso più elevate consentivano di eliminare il secondo stadio di conversione. Attualmente c'è una crescente tendenza a utilizzare i ricevitori a conversione diretta (zero-IF) dotati di demodulatore I/Q, che eseguono una conversione diretta dalla frequenza radio alla banda base dividendo il segnale in componenti in fase (I) e in quadratura (Q), i quali vanno sottoposti a campionamento sincrono e richiedono due ADC per ogni canale di ricezione.

- Sistemi di antenne avanzati, spesso definiti "antenne intelligenti" o MIMO (Multiple Inputs / Multiple Outputs), che utilizzano catene di (trasmettitori e) ricevitori multipli per sfruttare la diversità di fase, di frequenza o di codifica tra le singole antenne. I vantaggi consisto-

no in una maggiore velocità di sistema e di trasmissione massima dei dati, una larghezza della banda di trasmissione più elevata e una maggiore efficienza spettrale.

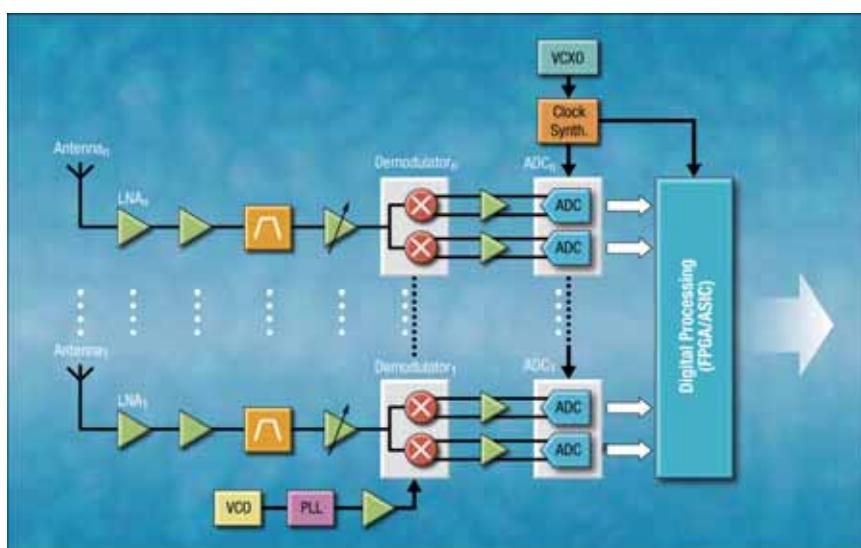

Entrambi questi concetti possono essere integrati in un sistema. Nella figura 3 è illustrato lo schema di principio di un ricevitore a conversione diretta con ricezione in diversità a due o più antenne. I ricevitori con diversità di ordine 2 sono stati ampiamente utilizzati ad esempio nelle stazioni base GSM e WCDMA, mentre con l'avvento del WiMAX si è affermata la

**Fig. 2 - Fasi evolutive dei ricevitori per telecomunicazioni**

**Fig. 3 - Ricevitore per telecomunicazioni con conversione diretta in banda base e campionamento I/Q in configurazione a diversità di antenna**

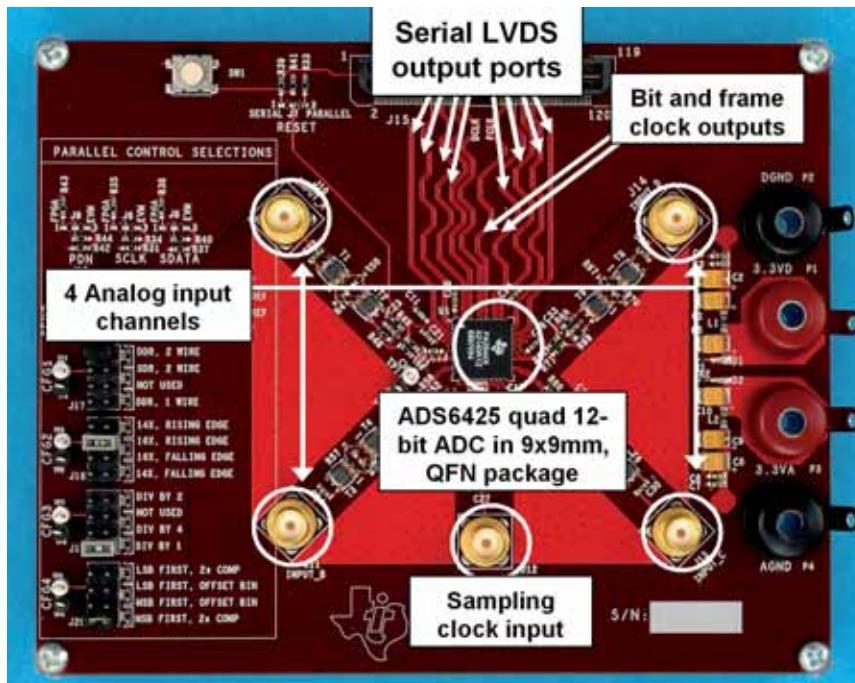

Fig. 4 - Scheda di valutazione per l'ADS6425, un ADC a 4 canali, 12 bit e frequenza di campionamento a 125 MSPS

### La nuova generazione di ADC adotta l'interfaccia seriale LVDS

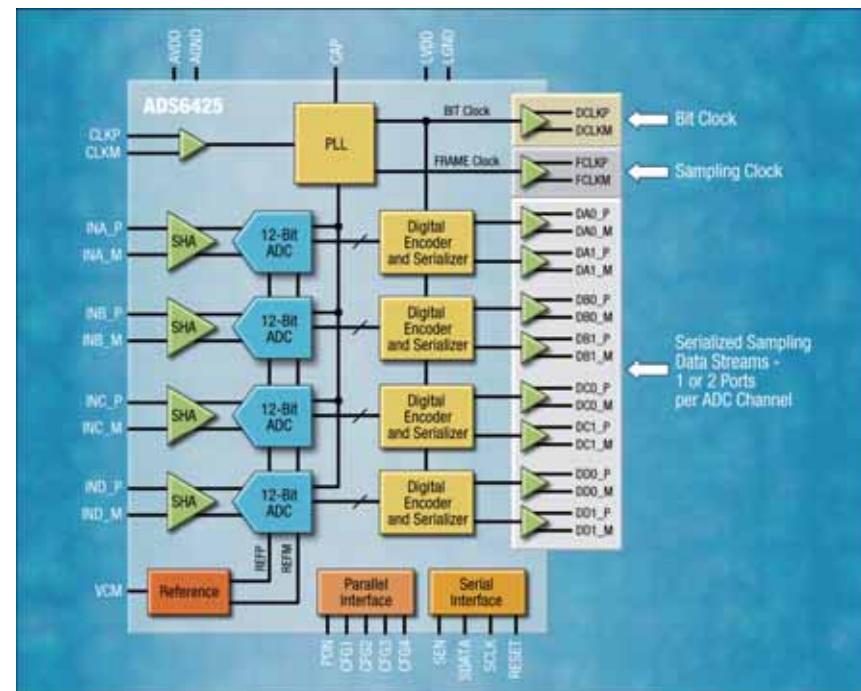

Un esempio di questa nuova generazione di ADC multicanale con interfaccia seriale LVDS è l'ADS6425 [2] di Texas Instruments, un convertitore analogico-digitale a 12 bit e 4 canali con una frequenza di campionamento massima di 125 MSPS. Questo modulo è il primo di una famiglia di ADC pin-to-pin compatibili a 12 e 14 bit con canale doppio o quadruplo e frequenze di campionamento da 80 a 125 MSPS.

Il principale vantaggio derivante dall'uso dell'interfaccia LVDS è un risparmio in termini di linee I/O e di dimensioni del package, grazie al quale è possibile inserire questo modulo in un package QFN a 64pin di soli 9x9 mm. La scelta di questa interfaccia rispetto ad altre interfacce seriali alternative comporta anche minori costi d'implementazione e un consumo energetico minimo grazie alla ridotta ampiezza del segnale differenziale dell'interfaccia LVDS, che consente di ottenere soli 410 mW per canale. Inoltre la segnalazione LVDS limita le

emissioni elettromagnetiche (grazie alle ridotte ampiezze di tensione) e presenta un'elevata tolleranza alle interferenze grazie alla configurazione differenziale. Esiste anche la possibilità di raddoppiare la corrente nominale di 3,5 mA dei driver LVDS in caso di lunghe tracce di interconnessione oppure, in alternativa, di ridurre la corrente di azionamento per ottimizzare ulteriormente il consumo e ridurre al minimo le emissioni radiate delle linee di segnali ad alta velocità.

L'interfaccia con configurazione 'clock-data-frame', illustrata nella figura 5, utilizza le seguenti linee differenziali:

- Dati seriali digitali campionati. Un ulteriore miglioramento rispetto alle generazioni precedenti è la possibilità di trasmettere i dati in uscita attraverso una porta seriale (frequenza max. di campionamento di 65 MSPS a 14 bit = 910 Mbps di velocità dati) o due porte seriali (frequenza max. di campionamento di 125 MSPS a 14 bit = 875 Mbps di velocità dati per porta) per ogni canale ADC, ampliando così ulteriormente la risoluzione massima e la frequenza di campionamento.

- Un clock di bit 6 volte superiore rispetto alla frequenza di campionamento dell'ADC, in caso di ADC a 12 bit, in modo da sincronizzare l'interfaccia dati seriale nella modalità DDR (Double Data Rate) sia sul fronte ascendente che su quello discendente.

- Un clock di sincronizzazione del frame identico alla frequenza di campionamento dell'ADC per segnalare al modulo ricevente l'inizio di una nuova parola di dati.

Ulteriori miglioramenti introdotti in questa nuova famiglia di convertitori includono:

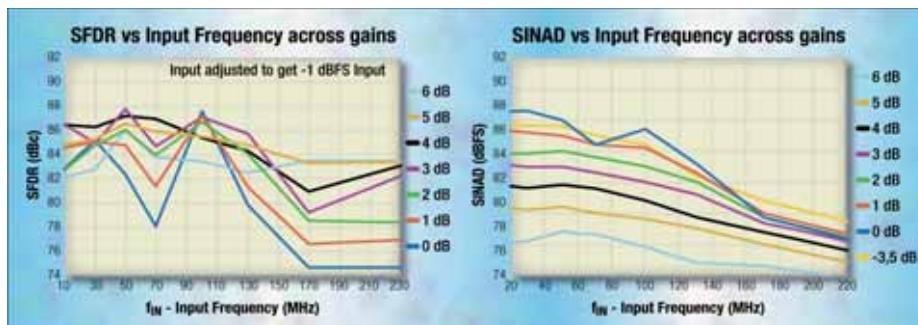

- Un buffer a guadagno programmabile per l'ingresso dei segnali, che consente di scalare il segnale in ingresso nell'ADC in modo approssimativo a passi di 3,5 dB oppure, a livello più accurato, a passi di 1dB in un intervallo da 0

diversità di ordine 4 e attualmente lo standard cinese TD-SCDMA utilizza sistemi di antenne intelligenti con diversità di ordine 8.

Questa maggiore densità di canali nei ricevitori per telecomunicazioni ha favorito l'impiego di ADC multicanale con uscite seriali per implementazioni a costo ridotto e ingombro limitato.

Allo stesso tempo, grazie ai bassi consumi di potenza degli ADC con campionamento IF e ai progressi nella tecnologia di connessione seriale è oggi possibile utilizzare i convertitori multicanale con interfaccia seriale LVDS per il campionamento IF, per risoluzioni più elevate (tipicamente 14 bit) e in applicazioni che richiedono maggiori frequenze di campionamento, come WiMAX (ad esempio 112 MSPS) e WCDMA (ad esempio 122,8 MSPS).

a 6 dB. Questo buffer permette un migliore utilizzo dell'intervallo in ingresso di 2 V picco-picco di fondo scala con segnali più piccoli. Inoltre consente a fronte di un lieve degrado nel rapporto segnale/rumore (SNR) un notevole miglioramento del SFDR (spurious-free-dynamic-range). In particolare nel caso di frequenze di ingresso elevate, questo modalità consente di ottimizzare il rapporto segnale/rumore e distorsione (SINAD).

- Un buffer a guadagno programmabile sull'ingresso a clock di campionamento. Poiché il contributo al jitter fornito dal clock di campionamento è maggiore in caso di ampiezze di clock ridotte, è consigliabile di operare con ampiezze del segnale di clock possibilmente ampie. Il buffer permette di amplificare il segnale di clock in ingresso, garantendo un funzionamento corretto anche con ampiezze di clock ridotte.

## I vantaggi della tecnologia seriale

L'impiego di interfacce seriali LVDS nei convertitori di dati offre molteplici vantaggi:

- Riduzione dello spazio richiesto dal package del convertitore di dati e dal cablaggio delle linee di I/O sulla scheda, con una conseguente semplificazione del layout e una potenziale riduzione degli strati della scheda. Ad esempio, per un ADC a quattro canali e risoluzione di 14 bit è oggi necessario un minu-

Fig. 5 - Convertitore A/D seriale con interfaccia di uscita "clock-data-frame" [2]

di dati ad alta risoluzione e quindi sia i convertitori che i moduli logici tendono a essere "I/O bound" piuttosto che "chip-size bound", cioè le dimensioni del package e quindi i relativi costi sono determinati essenzialmente dai pin I/O e non dalle dimensioni del chip.

- Semplicità di migrazione tra risoluzioni e frequenza di campionamento. L'interfaccia rimane identica, mentre le modifiche della risoluzione e della frequenza di campionamento sono gestite a livello software dal dispositivo ricevente.

- La possibilità di un doppio flusso di dati in uscita estende il campo di risoluzioni e di frequenze di campionamento possibili, e consente di supportare fino a 14 bit a 125 MSPS.

### Fonti di riferimento:

- [1] Scheda tecnica TI ADS5270 (<http://focus.ti.com/docs/prod/folders/print/ads5270.html>)

- [2] Scheda tecnica TI ADS6245 (<http://focus.ti.com/docs/prod/folders/print/ads6245.html>)

Fig. 6 - Ottimizzazione di SFDR e SINAD con guadagno del buffer in ingresso dell'ADC

Texas Instruments

[www.ti.com](http://www.ti.com)