18 EONews n. 434 - 25 MARZO 2005 attualità

## ➡ segue da pagina 16

## Gestione del traffico...

va (SR) definisce inoltre una finestra temporale nella quale è necessario che avvenga l'operazione completa di ritrasmissione di un pacchetto da parte del nodo Fibre Channel . il transito attraverso la rete di trasporto e la ricezione da parte del nodo Fiber Channel ricevente, e il transito inverso del pacchetto di acknowledgement lungo la rete fino al nodo che ha effettuato l'invio iniziale. Se si prende in considerazione il lato SO-NET/SDH della scheda di linea, si passa dalla problematica di garantire un controllo specifico sui flussi di dati dei clienti, a quella di permettere al fornitore di servizi di gestire la rete in modo efficiente. In questo articolo ne descriveremo due: la concatenazione virtuale (V-CAT) e lo schema per la regolazione della capacità del link (LCAS, Link Capacity Adjustment Scheme). La Virtual Concatenation (V-CAT) permette a un gestore di rete SONET/SDH di rendere disponibili in maniera preventiva dei canali distinti, con banda garantita, nell'ambito di un payload SONET/SDH e di assegnare ogni canale a un cliente diverso. La potenza del V-CAT deriva dal fatto che ogni canale viene suddiviso in diversi affluenti. In questo modo il gestore della rete decide, fino al livello massimo di granularità di un singolo affluente, come utilizzare la banda disponibile. Un altro protocollo che dà al fornitore di servizi il controllo sulla rete di trasporto, mantenendo la flessibilità necessaria per garantire ai clienti un servizio ottimale, è il Link Capacity Adjustment Scheme (LCAS). Lo LCAS opera sui canali V-CAT descritti in precedenza. Permettere al gestore di rete di trasferire banda da un canale a un altro, senza interferire sull'allocazione di banda dei restanti canali

## **Stazioni base wireless** con i **Platform FPGA**

Parallelismo, costi ridotti, flessibilità e bassa dissipazione: i vantaggi principali

ricavi legati alle infrastrutture wireless continuano ad essere interessati da una crescita straordinaria: secondo le stime sono passati da circa 27 miliardi di dollari nel 2003 a 35 miliardi di dollari nel 2004. Gli analisti ritengono tuttavia che il picco dei ricavi sia stato raggiunto nel 2004: Iricavi scenderanno a

27 miliardi di dollari nel 2005 e in ultima analisi si assesteranno attorno a 10 – 15 miliardi di dollari per la fine del decennio. La sfida per le stazioni base di prossima generazione consiste nel trovare il modo per ridurre i costi aggiungendo al contempo funzionalità per supportare nuovi servizi e protocolli e una maggiore flessibilità per mantenere un

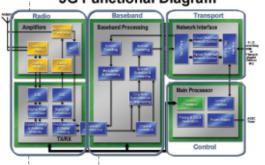

vantaggio competitivo e far fronte alle pressioni sul timeto-market. Per questo motivo i produttori di soluzioni wireless stanno progressivamente migrando verso componenti programmabili facilmente disponibili, come i dispositivi Platform FPGA All'interno di una stazione base wireless esistono moduli distinti che svolgono diverse funzioni come l'elaborazione a radiofrequenza ed in banda base, l'interfacciamento ed il controllo delle reti di trasporto, come mostrato in Figura 1. I progetti hanno tradizionalmente partizionato queste funzioni su ASIC, DSP ed altri componenti discreti, cercando di giungere sul mercato per primi al fine di aggiudicarsi fette di mercato. Le riduzioni dei costi erano ottenute tramite riprogettazioni successive, con nuove schede introdotte ogni 9 – 12 mesi. Tuttavia, con il rapido declino del prezzo medio di vendita delle stazioni base in corso dal 2001 (-80 % in appena 3 anni), questo approccio

na 3 anni), questo approccio

Wireless Base Station

3G Functional Diagram

Fig.1 Diagramma a

blocchi di un

modulo per

una stazione

base wireless

sta per essere rapidamente sostituito con lo sviluppo di progetti più economici e più flessibili che sfruttano la tecnologia FPGA per eliminare i costi globali di gestione dei dispositivi ASIC proprietari.

## LA STANDARDIZZAZIONE NELLE STAZIONI BASE WIRELESS

I produttori di infrastrutture wireless si trovano di fronte ad ardue decisioni. Essi devono partizionare la funzionalità richiesta per nuove caratteristiche attraverso le tecnologie disponibili, e al contempo sfruttare la proprietà intellettuale esistente e valutare il rischio

legato a nuove soluzioni per conciliare rischi ed incertezze con la flessibilità. Una soluzione completamente flessibile partizionata su DSP ed FPGA sarebbe ideale, ma non è sempre possibile. Una tecnica di transizione molto interessante consiste nell'inserire dispositivi discreti accanto agli ASIC esistential fine di supportare nuove funzionalità che non possono essere altrimenti aggiunte in modo tempestivo od economico. L'aggiornamento delle soluzioni esistenti per le versioni successive degli standard wireless (si pensi ad esempio alle iniziative OBSAI -RP3 e CPRI ed alle specifiche W-CDMA emanate dal consorzio 3GPP) può essere effettuato

> anche con un piccolo FPGA a basso costo È disponibile un'ampia scelta di blocchi di proprietà intellettuale per l'implementazione di funzionalità richieste dagli standard wireless: essi sono progettati per offrire una latenza d'elaborazione molto bassa. oltre ad una riduzione espressiva dei costi. dei rischi e dei consumi. Ouesta dicotomia fra costo e prestazioni che

impone di "offrire di più per meno" è stata ben risolta dalla legge di Muore ed è applicabile a tutti i dispositivi prodotti in volumi come ASIC DSP microprocessori e FPGA. Tuttavia, siccome diventa sempre più difficile rispettare la roadmap per le tecnologie deep submicron, il parallelismo intrinseco, la programmabilità ed il modello di business relativo agli FPGA si pongono come la soluzione più adatta per consentire l'innovazione e la differenziazione necessarie per soprav-

Andy Miller, Senior Manager Wireless Systems, DSP Division, Xilinx David Gamba, Senior Manager, Strategic Solutions Marketing, Xilinx

vivere in un mercato sempre più popolato da prodotti commodity. La roadmap per le tecnologie mobili offre una varietà di soluzioni e le stazioni base trarrebbero beneficio da una piattaforma di tipo programmabile comune. Gli FPGA costituiscono quindi una scelta logica quando entra in gioco la flessibilità, ma sono abbastanza convenienti? I requisiti di costi e di prestazioni impongono il ricorso di geometrie di processo sempre più miniaturizzate. La percezione dell'industria è che le geometrie di processo più miniaturizzate su silicio hanno portato ad un aumento della potenza statica dovuto ad una maggiore corrente di leakege nei transistor. In generale questo è vero, tuttavia la tecnologia a triplo ossido allo stato dell'arte ed i livelli superiori di integrazione DSP hanno reso possibili progressi significativi nella riduzione della dissipazione di potenza sia statica sia dinamica dei Platform FPGA di punta. La migrazione verso il nodo da 90 nm ha portato ad una riduzione del 50 % nella potenza statica e dinamica e sarà possibile ottenere ulteriori benefici con le generazioni da 65 nm e da 45 nm su wafer da 300 mm. Grazie al parallelismo intrinseco, ai costi ridotti di sviluppo, alla flessibilità ed ai bassi consumi gli FPGA sono idealmente posizionati per soddisfare i requisiti per l'elaborazione del segnale nelle stazioni base di prossima generazione. Il tool di sviluppo System Generator per DSP semplifica lo sviluppo e la messa a punto di progetti DSP ad alte prestazioni destinati alle stazioni base wireless. Il tool consente ai progettisti di lavorare all'interno di un ambiente di progettazione Matlab/Simulink, con le stesse prestazioni rispetto ad un'implementazione in linguaggi a livello più basso come VHDL.

# FPGA a basso costo pilotano l'innovazione dell'elettronica consumer

o stato attuale del mercato dell'elettronica di consumo (CE) sta costringendo i costruttori a rivalutare i modelli di sviluppo dei loro prodotti. I metodi tradizionali - basati sull'uso di ASSP o di ASIC custom per ottenere un costo finale più basso possibile – si stanno rivelando inadeguati nei confronti di una domanda in rapida evoluzione che mira a una crescente differenziazione dei prodotti. Proprio per questo, gli sviluppatori di prodotti CE stanno rapidamente orientandosi verso le soluzioni basate su logiche programmabili. Tali soluzioni consentono loro sia di rispondere al rapido cambiamento delle esigenze dei consumatori sia di offrire nuove dotazioni e nuove capacità. Questo trend è stato incoraggiato dalla recente proliferazione dell'offerta di FPGA a basso costo. I prodotti di maggior successo del mercato CE si trovano rapidamente a misurarsi con una massa di prodotti concorrenti proposti da alti costruttori. La repentina reazione della concorrenza provoca una rapida erosione dei prezzi e impedisce agli sviluppatori di ottenere dei ritorni apprezzabili da prodotti caratterizzati da un ciclo di vita utile sempre più breve. A questo si aggiunge la crescente popolarità dei formati digital media per contenuti audio e video (A/V): tutto questo ha provocato un crescente interesse verso gli apparati e i metodi destinati a erogare tali contenuti agli utilizzatori. I consumatori hanno variato gli investimenti in apparati A/V analogici

aspetto che gli sviluppatori di prodotti CE devono tenere in considerazione. In tal senso gli sviluppatori CE hanno delle grosse opportunità, benchè l'esatta natura, le capacità, e i prezzi dei prodotti che possaono avere successo in quest'area siano aspetti non ancora compresi a fondo. Tali condizioni impongono livelli di flessibilità e di agilità nello sviluppo dei prodotti che vanno ben oltre quanto possa essere garantito da ASSP e ASIC. Gli sviluppatori di prodotti CE utilizzano spesso gli ASSP per svolgere un vasto spettro di funzioni, tra le quali la codifica e la decodifica A/V, l'interfacciamento di connessione le traslazioni di formato e le conversioni. Fare affidamento esclusivamente sugli ASSP non consente però agli sviluppatori di differenziare in modo significativo i loro prodotti. Le soluzioni ASSP spesso sono in grado di svolgere anche funzioni correnti e per questo gli sviluppatori di prodotti CE preferiscono oprare per delle piattaforme ASIC, capaci di garantire la tutela della proprietà intellettuale (IP) e di conseguenza la differenziazione dei prodotti. Gli ASIC offrono anche il vantaggio di assicurare prezzi unitari estremamente bassi. Sfortunatamente, i lunghi tempi di sviluppo richiesti dagli ASIC portano a innovare e offrire prestazioni distintive nell'ambito di un mercato ormai saturo di prodotti simili o che ha già subito un cambiamento. Gli elevati oneri fissi di ingegneria associa-

continua a pagina 20 →

\*Bernd Riemann, Director of Hardware Engineering Pinnacle Systems

## attualità

## ➡ segue da pagina 19

## FPGA a basso costo...

ti agli ASIC rappresentano inoltre una barriera significativa che esclude gli sviluppatori che non possono affrontare tali investimenti o che non reputano prudente assumere rischi finanziari elevati in presenza di mercati dove i parametri per ottenere prodotti di successo non sono ancora delineati. Come risultato. gli sviluppatori CE stanno comprendendo che la realizzazione di soluzioni basate su logiche programmabili - in grado di garantire uno sviluppo rapido e flessibile ma anche una possibilità aggiuntiva di innovazione di prodotto a fronte di un investimento ingegneristico minimo rappresenti un'opzione particolarmente valida

I dispositivi logici programmabili (PLD) a basso costo sono attualmente utilizzati nell'ambito di un vasto spettro di prodotti CE. Tra questi spiccano televisori, DVD player, riproduttori portatili, set-top box, reti "smart home" e periferiche per computer. La flessibilità di un PLD a basso costo può tornare utile allo sviluppatore di un prodotto CE sotto molti aspetti. I costruttori di prodotti CE che integrano una logica programmabile nell'area appropriata del loro progetto possono sviluppare nuove prestazioni semplicemente modificando la programmazione del PLD. Questa capacità consente loro di offrire più versioni di uno stesso prodotto, lasciando la libertà di sviluppare nuovi modelli in risposta al mutare delle esigenze del mercato. A questo si aggiunge la possibilità di assicurare l'aggiornamento sul campo dei prodotti esistenti. Grazie a queste capacità, gli sviluppatori di prodotti CE possono sfruttare i vantaggi offerti dagli ASSP a basso costo per le funzioni più stabili, affidandosi alla logica programmabile per ottenere il giusto livello

di differenziazione. La differenziazione può abbracciare caratteristiche legate alla sfera audio o video, alla sicurezza, alle funzioni programmabili dall'utente o anche alle modalità operative. Un esempio di innovazione di questo tipo è il prodotto Studio MovieBox Deluxe di Pinnacle Systems.

MovieBox Deluxe è un apparato che consente di gestire vari formati video provenienti da fonti sia analogiche sia digitali. I dati possono essere importati in un PC per l'editing con il software Pinnacle Studio 9. Molti utilizzatori dispongono di contenuti video memorizzati su nastri analogici; altri dispongono di contenuti memorizzati in formati digital video (DV) immagazzinati in dispositivi – per esempio le videocamere digitali – dotati di interfacce IEEE 1394 (o FireWire). Purtroppo, i PC di questi utenti spesso non sono equipaggiati con una interfaccia IEEE 1394. MovieBox Deluxe è in grado di collegare tutte queste fonti video a un PC utilizzando una normale interfaccia USB (universal serial bus) 2.0. Successivamente all'editing, MovieBox Deluxe è in grado di assicurare la connessione tra il PC e una TV un VCR o una videocara digitale per la riproduzione o la memorizzazione del filmato. MovieBox Deluxe include varie interfacce, tra le quali ingressi e uscite RCA ed Svideo per dispositivi analogici e collegamenti IEEE 1394 per dispositivi digitali. Tutte queste connessioni - interfacciate al PC attraverso una connessione USB 2. 0 - sono gestire dagli

ASSP integrati in MovieBox Deluxe. Un FPGA Cyclone gestisce l'interazione tra gli ASSP. In funzione della fonte video coinvolta MovieBox Deluxe opera secondo una sola delle modalità che offre. Poichè il dispositivo può operare secondo una sola modalità alla volta Pinnacle ha deciso di sfruttare la riconfigurabilità dell'FPGA per predisporre il dispositivo Cyclone per lavorare secondo la modalità richiesta, in funzione del tipo di cavo connesso all'apparato. Il tempo richiesto per configurare l'FPGA – pochi millisecondi – non è percettibile da parte dell'utilizzatore ed è nettamente trascurabile rispetto al tempo necessario per inserire il cavo nell'apparato MovieBox Deluxe. Il progetto FPGA che ne è scaturito utilizza una quantità decisamente inferiore di risorse logiche (meno di un terzo del totale) altrimenti necessarie se Pinnacle avesse deciso di ricorrere a un dispositivo non-riconfigurabile. Pinnacle è stata in grado di utilizzare l'FPGA Cyclone più piccolo, il cui costo è circa un quinto del costo totale dei materiali utilizzati. Per ridurre ulteriormente i costi, gli ingegneri Pinnacle hanno deciso di memorizzare i file di configurazione dell'FPGA nel direttamente device driver MovieBox Deluxe del PC. Questo schema ha permesso di evitare il ricorso a una memoria di configurazione dedicata da integrare nell'hardware di MovieBox Deluxe, riducendo in tal modo gli ingombri, il numero di dispositivi e i costi. Sfruttando in un modo così innovativo la riconfigurabilità degli FPGA, Pinnacle ha mantenuto al minimo gli oneri produttivi. La valutazione compiuta da Pinnacle sulle soluzioni alternative non ha permesso di individuare una soluzione capace di garantire né i target di costo né l'aggressivo piano di sviluppo ottenuto con gli FPGA Cvlone.