Gli FPGA della serie Stratix II di seconda generazione di Altera sono stati ottimizzati per la progettazione e la produzione di SOPC (System-On-a-Programmable-Chip)

# Architettura FPGA della prossima generazione per accelerare la progettazione di SOPC

Ed Clarke Product marketing engineer (Altera)

In un mercato sempre più competitivo come quello elettronico, i costruttori stanno cercando di aumentare il livello di integrazione dei loro sistemi per ottimizzare prestazioni, dimensioni e prezzi. Per ottenere integrazioni sempre più spinte di solito si fa ricorso a due tipi di soluzioni: SOC (System-on-Chip) basati su ASIC e, sempre più fre-

quentemente, SOPC (System-On-a-Programmable-Chip) basati su logiche programmabili. Grazie alla disponibilità di dispositivi logici programmabili a elevate prestazioni, con le soluzioni di tipo SOPC è possibile ottenere il livello di integrazione desiderato senza incorrere negli svantaggi tipici delle soluzioni ASIC: lunghi tempi di sviluppo, oltre a rischi e costi elevati.

L'obiettivo della tecnologia SOPC è realizzare un sistema completo all'interno di un FPGA: l'attuale disponibilità di blocchi IP (Intellectual Property) ottimizzati permette ai progettisti di conseguire tale scopo in tempi brevi. Nel momento in cui si implementano tali progetti è indispen-

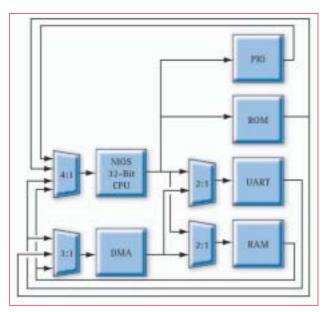

NIOS 32-bit CPU DMA RAM ROM UART PRO

Fig. 1- Progetto di un sottosistema di I/O formato da un processore embedded Nios a 32 bit, I/O paralleli, UART impiegato per espletare le funzioni di comunicazione e memorie RAM e ROM

sabile effettuare un attento bilancio tra costi di sviluppo, prestazioni ottenibili e prezzo che i clienti vogliono spendere per il conseguimento di tali performance. In passato, parecchie volte tali fattori non sono stati tenuti in considerazione, ostacolando quindi la diffusione delle soluzioni SOPC. Gli attuali FPGA (File Programmable Gate Array), grazie al sensibile incremento dei livelli di densità e alla consistente riduzione dei costi, permettono di implementare in maniera economica un sistema completo all'interno di un singolo chip programmabile. Oltre a ciò, con questi FPGA è possibile ridurre il tempo richiesto per il trasferimento di un progetto in produzione, in quanto non è più necessaria la realizzazione di prodotti campione per la verifica del progetto stesso.

L'approccio di tipo SOPC, infine, permette di apportare eventuali modifiche o migliorie in ogni momento, sia prima sia durante la produzione.

Un FPGA deve possedere determinate caratteristiche base se vuole essere impiegato come piattaforma per la realizzazione di un SOPC.

Esso deve disporre di sufficienti risorse in termini di routing, memoria, logica, I/O per poter garantire semplicità di progettazione, elevate prestazioni e ridotti tempi di sviluppo. Inoltre, è necessaria la presenza di blocchi IP capaci di accelerare lo sviluppo di applicazioni che prevedono l'impiego massiccio di funzioni DSP (Digital Signal Processing) come ad esempio elaborazione delle immagini, trasferimento dati e comunicazioni in modalità wireless.

L'FPGA in questione, inoltre, deve essere corredato da un insieme completo di tool di progettazione e di integrazione e disporre di adeguati kit di sviluppo al fine di minimizzare il ciclo di design.

Gli FPGA della serie Stratix II di seconda generazione di Altera sono

stati ottimizzati per la progettazione e la produzione di SOPC. Realizzati a partire dalla linea Stratix che si distingue per la presenza di parecchi innovazioni architetturali in termini di routing, memoria e blocchi DSP, gli FPGA della linea Stratix II sono caratterizzati da una struttura logica di nuova concezione ottimizzata per supportare l'implementazione di sistemi a elevate prestazioni in maniera efficiente.

Questa nuova struttura logica vede l'introduzione del modulo ALM (Adaptive Logic Module) che da un lato assi-

cura la flessibilità necessaria a supportare in maniera efficace funzioni di qualsiasi dimensione e dall'altro mette a disposizione numerose funzionalità per l'ottimizzazione del progetto.

Un tale incremento di flessibilità comporta una simultanea diminuzione dei livelli logici richiesti per la realizzazione di un progetto, un fattore di primaria importanza per gli attuali dispositivi in cui i ritardi imputabili alle interconnessioni risultano particolarmente critici.

Gli FPGA della serie Stratix II sfruttano questo aumento di flessibilità e i benefici derivati dal processo di produzione da 90 nm di TMSC per assicurare un miglioramento medio del 50% in termini di prestazioni rispetto agli equivalenti dispositivi Stratix di

prima generazione, a fronte di una diminuzione di costi del 40% a parità di densità. Il dispositivo di maggiori dimensioni della famiglia Stratix II integra 180K di LE (Logic Element – elementi logici) e 9,4 Mbit di memoria embed-

ded, assicurando livelli di integrazione di gran lunga superiori rispetto a quelli ottenibili con gli FPGA delle precedenti generazioni.

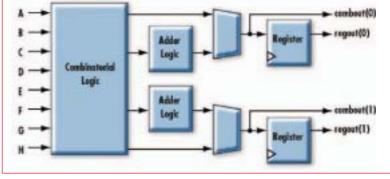

Fig. 2 - Il sistema di figura 1 riprogettato sfruttando il sistema di connessione Avalon

## Realizzazione di un SOPC mediante FPGA

Nell'esempio discusso in questo articolo viene illustrata la realizzazione di una soluzione SOPC mediante l'impiego di un FPGA della linea Stratix II di Altera. Il progetto riguarda un sottosistema di I/O formato da un processore embedded Nios a 32 bit, alcuni I/O paralleli usati a scopo di controllo, un UART impiegato per espletare le funzioni di comunicazione e risorse di memoria (RAM e ROM).

Al fine di ottimizzare l'ampiezza di banda disponibile della CPU è stato aggiunto un controllore DMA per garantire un trasferimento dei dati più efficiente tra il dispositivo UART e la memoria. In questo sottosistema relativamente semplice, rappresentato in figura 1 sono presenti sei blocchi connessi tra loro da un bus condiviso.

### Avalon: una struttura di commutazione efficiente

La realizzazione basata su Nios del sistema riportato in figura 1 può essere eseguita nel giro di pochi minuti mediante SOPC Builder, un tool che automaticamente costruisce la logica necessa-

ria per connettere i blocchi IP. Questo strumento effettua il collegamento tra i blocchi sfruttando Avalon, un bus semplice ed efficiente di natura completamente sincrona. Grazie a tale bus è possibile evitare l'impiego dei tradizionali collegamenti bidirezionali e dei buffer di tipo tri-state.

Le periferiche sono tutte connesse a ciascun dispositivo master presente nel sistema per mezzo di bus unidirezionali: ciò permette di eliminare dispositivi tri-state interni e contribuisce a semplificare la temporizzazione e a impedire l'insorgere di eventuali "colli di bottiglia" sul bus.

Il bus Avalon permette inoltre il trasferimento simultaneo tra coppie master e slave separate, caratteristica questa molto utile in sistemi contrad-

> distinti dalla presenza di flussi di dati multipli o particolarmente complessi. Nella figura 2 viene proposto il medesimo sistema di figura 1 riprogettato sfruttando il sistema di connessione Avalon. Si noti il collegamento tra ciascun blocco del sistema e i relativi multi-

plexer di ingresso relativi alle porte di lettura. Ogni connessione rappresenta un bus formato da segnali di controllo e da segnali di dati e di indirizzi unidi-

Fig. 3 - La struttura logica estremamente flessibile dei componenti la serie Stratix II sfrutta le potenzialità del modulo ALM

rezionali. Con un layout di questo tipo è possibile per un progettista comprendere con maggior precisione le modalità di transito dei flussi dei dati attraverso il sistema generato per mezzo di SOPC Builder e la sua implementazione a livello RTL.

Nell'esempio preso in considerazione i due dispositivi master del bus richiedono la presenza di multiplexer sul bus per poter supportare un bus di ingresso per ogni slave. Inoltre è necessario ricorrere ad altri multiplexer per

consentire l'accesso da parte di più master al medesimo dispositivo slave. Poiché in questo esempio si utilizza un bus dati a 32 bit, l'ingresso alla sola porta di lettura della CPU richiederà 32 multiplexer di tipo 4:1. All'aumento della complessità del dispositivo SOPC, con l'aggiunta di altri master sul bus, è indispensabile il ricorso a un numero maggiore di multiplexer di dimensioni più ampie.

I multiplexer sono richiesti per il supporto sia delle porte dei blocchi del sistema sia della CPU.

Infatti, una buona percentuale della logica presente nel sistema (fino al 20%) risulta composta da multiplexer destinati al controllo del flusso dei dati in transito nei pressi del core. L'ottimizzazione e l'incremento del throughput dei multiplexer avranno un impatto significativo sulle prestazioni complessive del sistema SOPC.

#### Realizzazione mediante FPGA

La mappatura del bus in un FPGA in questo sistema SOPC è un'operazione abbastanza semplice.

I conduttori che collegano i dispositivi master e slave possono essere trasportati senza problemi nella struttura di interconnessione dell'FPGA. La struttura di commutazione del bus Avalon sfrutta le potenzialità dei

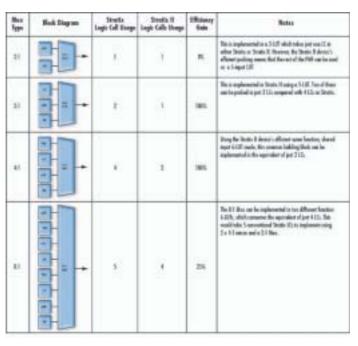

Tabella 1 - Guadagno di efficienza nell'implementazione dei multiplexer

dispositivi della serie Stratix II e di altri FPGA sviluppati da Altera per eseguire lo sbroglio dell'intero progetto in misura superiore al 95%. I multiplexer di ampie dimensioni vengono implementati sulle porte di lettura e scrittura che controllano le connessioni tra ciascun blocco. Gli ingressi di selezione dei multiplexer sono controllati dal dispositivo master in conformità all'indirizzo al quale si accede. Oltre a ciò, il dispositivo slave integra la logica di arbitrazione necessaria per il controllo delle richieste di accesso provenienti da più master. Tutta questa logica, multiplexer compresi, viene implementata in un circuito logico di tipo general purpose nell'FPGA. L'architettura dei componenti la serie Stratix II permette la realizzazione di queste funzioni in maniera molto più efficiente rispetto a quando possibile con le FPGA delle precedenti generazioni.

### Stratix II: un'architettura avanzata

La struttura logica estremamente flessibile dei componenti la serie Stratix II sfrutta le potenzialità del modulo ALM, dotato di otto ingressi, due uscite e due registri, che possono essere impiegati indipendentemente o assieme alle risorse della tabella di ricerca (LUT -Look Up Table) come riportato nella figura 3. Oltre a ciò è prevista la presenza di percorsi in retroazione, in cascata e di riporto veloce per consentire la realizzazione di funzioni di più ampie dimensioni e di addizionatori dedicati per il supporto di alberi di addizione di tipo ternario.

Le risorse LUT, di concezione decisamente innovativa, possono essere configurati in vari modi, come ad

esempio 7-LUT, 2 x 5-LUT con due ingressi condivisi, 2 x 4-LUT per garantire la compatibilità "all'indietro" con i dispositivi Stratix della prima generazione, o sfruttando una qualsiasi combinazione come ad esempio 3-LUT + 5-LUT.

Uno dei principali vantaggi legati alla disponibilità di una tabella di ricerca di ampie dimensioni è la possibilità di implementare multiplexer in maniera estremamente efficiente, come evidenziato nella tabella 1.

L'efficienza insita nell'architettura dei dispositivi della serie Stratix II si può facilmente comprendere considerando il multiplexer 4:1 a 32 bit utilizzato nel SOPC utilizzato come esempio in questo articolo: il componente può essere realizzato impiegando solamente 32 LE, ovvero la metà degli elementi logici richiesti dalle precedenti architettura.

#### Sistemi reali

La compilazione del sistema SOPC oggetto dell'articolo permette di evidenziare i vantaggi legati al supporto di funzioni di ampie dimensioni. Un dispositivo della linea Stratix II permette di integrare tale sistema in un circuito logico equivalente a 1944 LE, un numero nettamente inferiore rispetto ai 2695 LE necessari per

un'implementazione mediante dispositivi Stratix. I 751 elementi logici risparmiati rappresentano un aumento dell'efficienza pari al 75%, senza dimenticare il guadagno del 32% in termini di f<sub>MAX</sub>, che in questo caso può arrivare fino a 140 MHz. Gli aumenti delle prestazioni e il miglioramento dell'efficienza permettono di realizzare, in maniera affidabile, progetti di sistemi SOPC basati su FPGA sempre più complessi.

Naturalmente, parecchi sistemi reali saranno contraddistinti da un grado di complessità superiore rispetto a quello del SOPC discusso in questo articolo. In tali sistemi, molto spesso è richiesta la presenza di multiplexer di dimensioni più ampie.

Con il software di progettazione Quartus II di Altera è possibile realizzare questi multiplexer di più ampie dimensioni utilizzando mux 8:1 come blocchi base, minimizzando nel contempo il numero di livelli logici richiesti al fine di preservare i vantaggi in termini di prestazioni. I multiplexer sono blocchi base molto comuni in parecchi sistemi caratterizzati da percorsi dati variabili. I sistemi basati su DSP, dove la multiplazione dei blocchi è di tipo a divisione di tempo, richiedono la disponibilità di blocchi multiplexer, così come la richiedono parecchi standard di I/O.

Ciascun protocollo che integri parole di controllo e operi a elevata velocità necessita della logica per l'inserimento e l'eliminazione delle parole di controllo dal flusso dei dati. Le operazioni di inserimento e cancellazione, così come quelle necessarie per l'allineamento dei dati all'interno o all'esterno del flusso richiede l'impiego di un barrel shifter, anch'esso composto da multiplexer di diverse ampiezze.

#### **Considerazioni conclusive**

I SOC si stanno imponendo come la miglior soluzione per i progettisti che intendono realizzare sistemi che devono abbinare dimensioni ridotte, prestazioni spinte e prezzi competitivi. I SOC assicurano significativi vantaggi in termini di integrazione – che si traduce in una minimizzazione degli ingombri sulla scheda – affidabilità, prestazioni e costi.

L'incremento, in termini sia di densità sia di prestazioni, stanno favorendo l'utilizzo dei dispositivi logici programmabili per la realizzazione di SOPC, sistemi che assicurano ulteriori vantaggi in termini di aumento di flessibilità e diminuzione dei costi di sviluppo, dei rischi e del time to market. I nuovi FPGA della serie Stratix II di Altera fanno ricorso a un'architettura di concezione innovativa che garantisce il raddoppio della densità e la riduzione dei costi pari a circa il 40% rispetto agli FPGA delle precedenti generazioni. Tali peculiarità favoriranno senza dubbio la diffusione dei sistemi SOPC in nuovi settori applicativi.

Altera readerservice.it n.04