Le schede a processore in formato VME di MEN disponibili fino al 2032

-

- Tweet

- Pin It

- Condividi per email

-

Grazie a un bridge PCIe-VME basato su FPGA, i nuovi SBC VME realizzati da MEN Mikro Elektronik installati presso il CERN garantiscono tutti i vantaggi legati alla disponibilità sul lungo termine delle installazioni esistenti.

MEN ha sviluppato per il CERN una nuova scheda in formato VME equipaggiata con processori della serie Xeon D di Intel. Grazie a un bridge tra PCIe e VME64x (PCIe-VME64x) basato su FPGA di tipo open source, le apparecchiature per l’attuale acceleratore di particelle possono essere aggiornate in modo da sfruttare le prestazioni offerte dai più moderni processori e rimanere operative ancora per molti anni. Il CERN prevede di utilizzare il bus VME fino al “pensionamento” dell’acceleratore di particelle (LHC) pianificata per il 2032.

Fondato nel 1954, il CERN è il più grande centro di ricerca a livello mondiale che si occupa di fisica delle particelle. Al giorno d’oggi, più di 2.500 dipendenti e oltre 12.000 scienziati ospiti provenienti da 85 Nazioni conducono ricerche avanzate sui blocchi base che compongono l’Universo. L’apparecchiatura probabilmente più nota è l’acceleratore di particelle LHC (Large Hadron Collider) che con i suoi 27 chilometri di diametro è la macchina più grande del mondo entrata in funzione nel 2008. Uno dei quesiti che si cerca di risolvere con questa apparecchiatura è comprendere le ragioni per cui il nostro Universo è formato principalmente da materia e non è invece suddiviso in parti uguali tra materia e antimateria. Per cercare di fornire una risposta a questa e a molte altre domande sono utilizzate le apparecchiature più avanzate al momento disponibili e, anno dopo anno, sono stati effettuati ingenti investimenti. Ovviamente, il mantenimento dell’infrastruttura esistente negli anni a venire è un aspetto di fondamentale importanza.

Fig 1): Circa 900 crate basati su VME sono installati al CERN per controllare gli acceleratori nel corso dei vari esperimenti

Crate flessibili per l’acquisizione dati e il controllo dell’acceleratore

Si considerino ad esempio le migliaia di cosiddetti “crate” (o cestelli) che nel corso degli anni sono stati installati nei numerosi acceleratori di particelle presenti al CERN (Fig. 1). Installati nell’infrastruttura di supporto di vari rilevatori di particelle, essi sono solitamente utilizzati per ospitare l’elettronica di trigger e di acquisizione dati[1]. La configurazione tipica di questi crate è quella basata su slot con backplane e moduli liberamente configurabili. Questi sistemi elettronici di concezione modulare rappresentano la soluzione ideale per isituzioni scientifiche come appunto il CERN, in quanto consentono il riutilizzo dei singoli circuiti in molteplici sistemi e in svariate configurazioni. Una volta terminato l’esperimento, i crate vengono riutilizzati per nuovi esperimenti in una configurazione differente, garantendo in tal modo la protezione dell’investimento sul lungo periodo.

Un tipo di questi crate è basato sul bus VME (le cui prime specifiche risalgono al 1981), uno standard che nel corso dei decenni è stato sottoposto a continui miglioramenti e aggiornamenti. Attualmente al CERN vengono utilizzati oltre 900 crate di questo tipo, principalmente per il controllo degli acceleratori. Crate in differenti configurazioni sono impiegati per l’acquisizione dei dati degli esperimenti e degli acceleratori. Nell’esperimento LHCb (ideato per scoprire cosa sia accaduto dopo il Big Bang che abbia consentito alla materia di sopravvivere e creare l’Universo che abitiamo), per esempio, essi vengono usati per pre-elaborare parte dei dati grezzi provenienti da circa 1 milione di sensori in modo tale che gli scienziati possano ricevere solamente i dati pertinenti alle loro analisi. Ulteriori crate sono presenti in numerosi altri rilevatori del CERN come ATLAS, CMS, ALICE, ISOLDE e TOTEM, espletando in alcuni casi compiti completamente differenti. Come d’altronde accade per qualsiasi altro sistema basato su backplane, il loro impiego è estremamente flessibile.

Nuovi crate per nuove sfide

Poichè i compiti variano in funzione del singolo esperimento, nuove configurazione vengono sviluppate su base continuativa al fine di garantire le migliori prestazioni di elaborazione. Nel 2016, solo per gli acceleratori sono entrati in funzione 50 nuovi crate. Inoltre è già prevedibile che circa 200 nuovi crate saranno installati durante il cosiddetto “Long Shutdown” previsto nel biennio 2019-2020: durante questa pausa saranno riparate e ammodernate tutte le apparecchiature.

Nel caso dei sistemi basati su VME sorge il problema che i processori non supportano in modo nativo la comunicazione su questo bus. Le schede a processore devono quindi fornire un “ponte” (bridge) tra PCIe e VME64x (PCIe-VME64x) per l’interfacciamento con il bus VME. I componenti discreti erano disponibili solo da un numero ridotto di costruttori mentre il principale fornitore aveva annunciato la fase di EOL (End Of Life) per il componente attualmente utilizzato (TSI148). L’entità del problema appare chiara se si considera il numero di computer su scheda singola (SBC – Single Board Computer) con bus VME installati al CERN: attualmente presso questo centro di ricerca vi sono più di 900 SBC basati su VME di MEN Mikro Elektronik equipaggiati con processori Intel® Core™ Duo e Core™ 2 Duo. Anche se si tratta di un numero sicuramente interessante per schede di questo livello qualitativo, il volume non giustifica sicuramente la produzione di un componente discreto “ad hoc”. Di conseguenza il Beams Department/Control Group (BE/CO) del CERN era alla ricerca di alternative sostenibili per gli anni successivi e aveva indetto una nuova gara d’appalto.

Alla ricerca di una nuova soluzione di bridging per il bus VME64x

Nella gara d’appalto erano specificate tre possibili opzioni per effettuare il “bridging” tra PCI/PCIe e VME64x. La società che si fosse aggiudicata l’appalto doveva:

- disporre di uno stock di chip TSI148 suffiente a garantire la realizzazione del numero di schede previste dal contratto, oppure

- utilizzare Tundra Universe II, il predecessore di TSI148, o ancora

- Impiegare la tecnologia FPGA. In questo caso il CERN richiedeva a concorrenti di rendere disponibile l’intero codice VHDL utilizzato per questo progetto basato su FPGA attraverso una licenza GPL3 (o successiva).

Oltre alle due prime opzioni, abbastanza ovvie, il CERN era a conoscenza di aziende in grado di implementare bridge VME mediante FPGA. Gli SBC della precedente generazione che erano utilizzati al CERN (ovvero prima delle schede basate sul chip TSI148) erano equipaggiati con processori della serie PowerPC corredati da un FPGA per l’interfacciamento con il bus VME. Con la terza opzione prevista dalla gara di appalto i responsabili del CERN speravano che almeno una delle società concorrenti fosse pronta a rendere disponibile la propria implementazione in modalità open source. In ogni caso, per garantire una gara equa, il CERN non aveva espresso alcuna preferenza relativamente alle tre opzioni possibili. La scela finale era basata sul prezzo delle offerte presentate. In definitiva, il vincitore del contratto satebbe stata la società che proponeva il miglior prezzo.

Il bridge tra PCIe e VME64x di tipo open source è ora disponibile

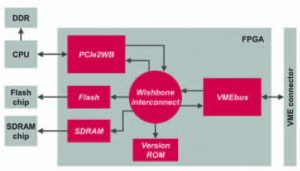

Il risultato della gara d’appalto ha portato alla scelta di una soluzione basata sulla tecnologia FPGA (Fig. 2) che rispettava i vincoli imposti per cui tutti i codici sorgente VHDL sono ora disponibili sotto una licenza GPL3 (o successiva), mentre i package dei driver del sistema operativo Linux sono disponibili su licenza GPL2 (o successiva) sulla pagina del progetto di questo bridge dell’OHR (Open Hardware Repository[2]).

Fig 2 – Con l’introduzione e il rilascio su licenza GPL del bridge PCIe-VME64x basato su FPGA, MEN Mikro Elektronik è stata in grado di assicurare la disponibilità sul lungo termine dei crate che utilizzano il bus VME per un periodo superiore a quello di utilizzo previsto al CERN

Il fatto di poter utilizzare un bridge PCIe-VME64x di tipo open source rappresenta un notevole passo in avanti non solo per il CERN, ma anche per le istituzioni di tutto il mondo che ancora utilizzano il bus VME. In primo luogo, i progettisti del CERN non sono più vincolati a uno specifico produttore. Anche nel caso in cui l’FPGA attualmente utilizzato diventasse obsoleto, l’accesso ai sorgenti VHDL consente di effettuare il porting del bridge PCIe-VME su un altro FPGA. Poichè il progetto è di tipo open source, qualsiasi istituzione o società può non solo acquistare un prodotto aggiornato con quello specifico tipo di bridge, ma anche realizzare qualsiasi altro SBC con bus VME sfruttando la medesima tecnologia di bridging per questo bus. L’impiego degli stessi bridge VME sugli SBC significa anche che i driver del kernel Linux e le API VME dello spazio utente sono le medesime per tutte le istituzione e le aziende. Ciò garantirà in futuro a tutti i progettisti di collaborare in maniera più efficiente nel “mondo” VME e di godere di una maggiore libertà di condividere e riutilizzare i driver del kernel Linux per le schede slave VME che i progettisti del CERN, ad esempio, sviluppano in autonomia.

Un contributo fondamentale allo sviluppo della nuova FPGA

MEN Mikro Elektronik è stata l’azienda che si è fortemente impegnata a collaborare con il CERN nella progettazione, collaudo e validazione di un bridge tra PCIe Gen3 e i sistemi VME a 64 bit. La società ha cooperato con il CERN non solo nelle fasi di validazione e di test, ma anche nella pubblicazione del codice sorgente con licenza open source del bridge PCIe-VME che converte le operazioni di lettura e scrittura nello spazio di indirizzamento di PCIe in transazioni di lettura e scrittura sul bus VME. Esso agisce da un lato come endpoint PCIe e come master del bus VME dall’altro. Il bridge può generare trasferimenti SCT (Single Cycle Transfer, ovvero a ciclo singolo) o BLT (Block Transfer, ovvero a blocchi).

Attualmente sono supportate le seguenti tipologie di accesso:

- Trasferimenti SCT: modalità di indirizzamento A16, A24, A32 con qualsiasi ampiezza dei dati D8, D16, D32 (8, 16 o 32 bit)

- Trasferimenti BLT: A24D16, A24D32, A32D32 oltre a trasferimento MBLT (BLT multiplato) A24D64 e A32D64

- Accesso allo spazio di configurazione CR/CSR

I trasferimento a blocchi sul bus VME sono eseguiti da un engine DMA (Direct Memory Access), dove I blocchi di dati sono trasferiti tra la memoria di sistema e il bus VME, senza far intervenire la CPU. Oltre a ciò, è possibile utilizzare la modalità DMA nei trasferimento a ciclo singolo, che risulta particolarmente utile per le schede connesse che non supportano le modalità di accesso BLT. In generale, si tratta del modo più veloce ed efficiente per scambiare più parole di dati, poichè la CPU è libera di svolgere le sue normali operazioni fino a quando l’engine DMA non ha terminato il task programmato. Il bridge in questione supporta anche altre funzionalità che sono state aggiunte nelle estensioni di VME64x. Esso è in grado di utilizzare i pin di indirizzamento geografico e generare un particolare tipo di accesso A24 per leggere e scrivere nello spazio di configurazione CR/CSR degli slave VME installati nel medesimo crate. Anche se attualmente non è supportata nessuna delle nuove modalità di trasferimento veloci (2eVME, 2eSST), queste potrebbero venire implementate in futuro nel caso fossero richeste dalle schede slave VME di prossima introduzione: questa eventualità, in ogni caso, è già stata presa in considerazione dagli specialisti di MEN. Oltre a ciò, il modulo per bus VME implementato da MEN può agire sia come master VME sia come slave VME. Questa dualità consente il suo utilizzo non solo negli SBC VME che operano come master, ma anche di impiegarli su schede di I/O e altre schede periferiche collegate come slave. Anche se, a onor del vero, nelle applicazioni che adottano SBC VME, la configurazione è focalizzata unicamente sull’utilizzo in modalità master).

Attualmente il progetto di questa soluzione di bridging occupa solamente il 30% circa dell’area dell’FPGA della linea Cyclone di Intel, quindi esiste spazio più che a sufficienza per l’implementazione di nuove funzionalità aggiuntive (come i trasferimenti ad alta velocità sfruttando i protocolli 2eVME e 2eSST).

Disponibilità garantita sul lungo periodo

Con il rilascio della specifica e l’installazione e messa in funzione delle prime schede con il nuovo bridge PCIe-VME64x basato su FPGA, il CERN ha raggiunto un importante traguardo per quanto concerne la disponibilità sul lungo periodo per propri crate basati su VME utilizzati per l’acquisizione dati e il controllo dell’acceleratore. Si tratta in ogni caso di un obiettivo molto importante per tutti gli altri utilizzatori di sistemi basati su VME, poichè anche per questi ultimi è ora garantita la disponibilità sul lungo periodo di una soluzione basata su logica programmabile. In base ai dati di una recente ricerca, il mercato per le nuove schede è destinato a generare un volume di affari superiore a 200 milioni di dollari nel 2020 (Fig. 3).[3]

Fig 3: Anche se il mercato delle schede VME è in declino, la società di ricerche di mercato IHS stima che esso genererà un volume di affari superiore a 200 milioni di dollari all’anno, che corrisponde alla vendita di oltre 250.000 schede (assumendo un prezzo medio per scheda di 750 dollari) (fonte IHS)

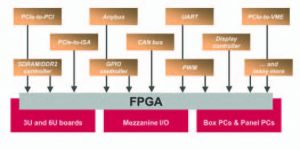

Questo progetto è una chiara dimostrazione del know-how acquisito da MEN Mikro Elektronik nell’utilizzo di FPGA in sistemi di elaborazione embedded standardizzati e delle sue competenze nel campo delle schede CPU con bus VME. Con questo bridge PCIe-VME, gli utenti possono sfruttare tutti i vantaggi legati alla disponibilità sul lungo termine delle installazioni esistenti. MEN Mikro Elektronik è anche in grado di offrire, a richieste, soluzioni simili, come ad esempio bridge PCIe-PCI o perfino PCIe-ISA, grazie ai quali viene prolungata la disponibilità dell’hardware di tipo “legacy” degli OEM, garantendo in tal modo un ritorno degli investimenti ancora migliore. Oltre alle soluzioni di bridging per i bus “legacy” interni finalizzate a garantire la disponibilità sul lungo termine, la società è anche in grado di realizzare bridge (sempre basati su FPGA) per interfacce esterne e bus tra cui UART, bus CAN o controllori QSPI che utilizzano l’interfaccia SPI (Fig. 4). Ciò consente ai clienti OEM di sviluppare diverse versioni in maniera estremamente economica. Il progetto di una singola scheda CPU, ad esempio, può essere utilizzata in applicazioni completamente differenti tra di loro. Anche con piccoli lotti di produzione, è possibile soddisfare le esigenze di un numero molto maggiore di applicazioni – come nel caso delle soluzioni a livello di sistema con differenti bus di campo o varie versioni di Ethernet industriale. Anche le soluzioni che hanno requisiti di migrazione, come accade nel caso dell’ingegneria ferroviaria o nel settore della costruzione di aeromobili, possono trarre notevoli vantaggi. Gli OEM possono usare una singola piattaforma in tutte le sue versioni, il che semplifica notevolmente le operazioni di assistenza, documentazione e certificazione.

Fig 4 – MEN Mikro Elektronik è in grado di realizzare una vasta gamma di soluzioni basate su FPGA per sistemi di elaborazione embedded standard e piattaforme customer-specific.

La prima scheda con il nuovo bridge

La prima scheda equipaggiata con il nuovo bridge basato su FPGA per il bus VMU utilizzata al CERN è il mod. A25 di MEN Mikro Elektronik (Fig. 5). Essa ospita la CPU Xeon D-1500 di classe server di Intel e, oltre all’FPGA, dispone di numerose altre funzionalità ed è offerta a un prezzo competitivo. Grazie a una singola scheda come questa è possibile realizzare sistemi dimensionalmente compatti, assicurare il funzionamento sul lungo periodo senza ricorrere al raffreddamento ad aria forzata ed espletare un gran numero funzioni di elaborazione. Dotata di due porte USB 3.0, di tre porte (max.) Gigabit Ethernet e di due porte COM RS-232 sulla parte frontale, mette a disposizione tutte le funzionalità fondamentali di un computer industriale multi-uso.

Fig 5 – L’SBC (Single Board Compuer) A25 di MEN Mikro Elektronik corredato dal bridge PCIe-VME64x è equipaggiato con la CPU Xeon D1500 di classe server di Intel e abbina un gran numero di funzionalità a un costo competitivo

Particolarmente ricca la dotazione di memoria, che comprende fino a 8 Gbyte di SDRAM DDR4 (con ECC) e memoria flash, oltre a slot per schede microSD e dischi mSATA per ulteriori espansioni. La scheda A25 può essere equipaggiata con una scheda mezzanino XMC/PMC e uno slot per schede mini PCI Express, mettendo così a disposizione ulteriori I/O sulla parte frontale (XMC/PMC) per il supporto di funzionalità grafiche, memorie di massa o porte Ethernet aggiuntive. Lo slot PMC supporta supporta moduli fino a PCI-X 64 bit/133 MHz, mentre lo slot XMC è controllato da un link PCI Express x8. L’espansione di tipo modulare resa possibile dalle schede mezzanino di I/O presenti su un SBC consente di configurare sistemi “su misura” sfruttando componenti basati su standard aperti, con conseguente riduzione sia dei tempi richiesti per l’integrazione sia dei costi. La scheda A25 può operare nell’intervallo di temperatura compreso tra -40 e +60 °C. Estremamente robusta, essa può resistere a sollecitazioni e vibrazioni di notevole entità grazie al fatto che tutti i componenti sono saldati sulla scheda, requisito indispensabile per assicurare affidabilità di funzionamento e maggior durata operativa del prodotto.

[1] https://en.wikipedia.org/wiki/Modular_crate_electronics

[2] https://www.ohwr.org/projects/pcie-vme-bridge

[3] http://embeddedtechtrends.com/2017/PDF_presentations/M06%20-%20IHS%20Markit.pdf

Gunther Gräbner - Product Line Manager (MEN Mikro Elektronik) Grzegorz Daniluk - Project Leader & Electronics Engineer Adam Wujek - Low-level Software Engineer (CERN)

Contenuti correlati

-

Applicazioni del calcolo quantistico

In questo articolo verranno introdotte alcune applicazioni dell’informatica quantistica e le relative sfide Leggi l’articolo completo su EO 508

-

Disponibili presso Rutronik i moduli Silex SX-PCEAX tri-band Wi-Fi 6E 2×2 PCIe

Destinato a WLAN per applicazioni mission-critical esigenti, il nuovo modulo Silex SX-PCEAX Tri-Band Wi-Fi 6E 2×2 PCIe, disponibile presso Rutronik, è stato dotato della banda a 6 GHz oltre a quelle a 2.4 e a 5 GHz....

-

FPGA MachXO3 a densità ultrabassa

Lattice Semiconductor ha annunciato la famiglia di FPGA (Field Programmable Gate Array) MachXO3 a densità ultrabassa; si tratta della piattaforma programmabile di dimensioni più piccole e costo più basso per I/O al mondo, pensata per espandere le...

-

Prima Electro si aggiudica la fornitura di 2700 convertitori di potenza per l’LHC Quench Protection System del CERN

A seguito di un bando di gara internazionale, che ha visto partecipare le principali aziende europee operanti nel settore dell’elettronica, Prima Electro si è aggiudicata la fornitura di 2700 convertitori di potenza AC-DC, per un valore complessivo di 500.000...

-

Il nuovo standard PCIe disegna l’ecosistema mobile

L’evoluzione dell’ecosistema mobile è direttamente collegato all’andamento degli standard PCIe. Il 25 giugno scorso il PCIe Special Interest Group Developers Conference ha spostato l’attenzione al Mobile Express o M-PCIe, annunciandone i risultati del suo lavoro con una...

-

Altera: SDK per l’elaborazione di video ‘beyond HD’

Altera ha annunciato l’introduzione di un kit per lo sviluppo di sistema ad alte prestazioni in grado di gestire formati e risoluzioni ‘beyond HD’ (ovvero oltre l’alta definizione) destinato a utilizzatori impegnati nella...

-

Micron acquisisce Virtensys

Micron Technology ha raggiunto un accordo per l’acquisizione di Virtensys, azienda privata specializzata nello sviluppo di soluzioni di condivisione su bus PCIe, con sedi a Manchester (Inghilterra) e Beaverton...

-

PCI Express punta al raddoppio

PCI-SIG (Special Interest Group) sta lavorando alla definizione delle specifiche della quarta generazione dello standard PCI Express. Quella che dovrebbe essere l’ultima versione per connessioni in rame, prima del prevedibile passaggio alla fibra...

-

IDT: bridge per la conversione di protocollo

Integrated Device Technology ha presentato il primo bridge per la conversione dal protocollo PCI Express Gen2 al protocollo Serial RapidIO (S-RIO) Gen2, che permette di estendere le applicazioni dei cluster multiprocessore interconnessi tramite RapidIO agli ambienti che...

Scopri le novità scelte per te x

-

Applicazioni del calcolo quantistico

In questo articolo verranno introdotte alcune applicazioni dell’informatica quantistica e le relative sfide Leggi l’articolo completo su...

-

Disponibili presso Rutronik i moduli Silex SX-PCEAX tri-band Wi-Fi 6E 2×2 PCIe

Destinato a WLAN per applicazioni mission-critical esigenti, il nuovo modulo Silex SX-PCEAX Tri-Band Wi-Fi 6E 2×2 PCIe,...

News/Analysis Tutti ▶

-

Nuovo stabilimento di LEM in Malesia

LEM ha inaugurato un nuovo stabilimento per semiconduttori nello stato di Penang (Malesia), frutto...

-

EET Group presenta il suo nuovo configuratore rack

EET Group ha realizzato un configuratore online per rack progettato per semplificare la ricerca...

-

L’Industria 5.0 in un sondaggio di element14 Community

Farnell ha recentemente condotto un sondaggio della element14 Community per valutare l’opinione attuale del...

Products Tutti ▶

-

Un nuovo condensatore MLCC da Samsung Electro-Mechanics

Samsung Electro-Mechanics ha presentato CL32C223JIV1PN#, un nuovo condensatore ceramico multistrato (MLCC) ad alte prestazioni...

-

Microchip facilita l’integrazione USB nei sistemi embedded

Microchip Technology ha presentato la famiglia di microcontroller AVR DU con funzionalità USB (come...

-

Microchip migliora la sicurezza dei prodotti IoT

Microchip Technology ha ampliato la sua offerta Trust Platform aggiungendo ECC608 TrustMANAGER con Kudelski...