Keysight introduces Chiplet PHY Designer for simulating D2D to D2D PHY IP supporting the UCIe standard

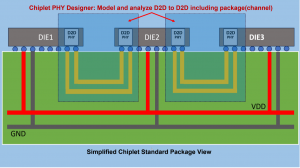

Keysight Technologies introduces Chiplet PHY Designer, the latest member in its family of high speed digital design and simulation tools that provides die-to-die (D2D) interconnect simulation, which is a key step in verifying performance for heterogeneous and 3D integrated circuit (IC) designs commonly referred to as chiplets. The new electronic design automation (EDA) tool is the industry’s first to provide in-depth modeling and simulation capabilities that enable chiplet designers to rapidly and accurately verify that their designs meet specifications of the Univeral Chiplet Interconnect Express (UCIe) standard.

UCIe is emerging as the leading chiplet interconnect specification in the semiconductor industry. It is an open standard that defines the interconnect between chiplets within an advanced 2.5D or 3D package. UCIe is in process of being supported or adopted by many of the top semiconductor equipment and EDA tool vendors as well as foundries and chiplet designers.

Niels Faché, Vice President and General Manager, Keysight EDA, said: “Our high-speed digital simulation team capitalized on its understanding of the shift left challenges presented by SerDes PHYS. They have applied these learnings to the chiplet domain to extend success of our standards-based simulation strategy to UCIe. Interconnect modeling is critical to system design and performance. Chiplet PHY Designer accelerates validation of chiplet subsystems, from one D2D PHY through interconnect channels to another D2D PHY, much earlier in the design cycle. It enables 3D IC designers to solve critical interconnect performance problems improving predictive virtual prototyping to speed time-to-market.”