Timing closure e sfide di progettazione per geometrie da 45 nm e oltre

Il problema legato al signoff delle temporizzazioni può essere considerato come un microcosmo rappresentativo sia del cambiamento dell’industria EDA sia della sua evoluzione

L’innovazione è la chiave di volta dell’industria dei semiconduttori, responsabile degli enormi cambiamenti avvenuti in tutti i settori, dalla progettazione alla fabbricazione, dall’assemblaggio al test.

Nel campo della progettazione, i requisiti fondamentali di innovazione stanno cambiando e stanno estendendo la propria portata. Un esempio è la design closure, dove le soluzioni dedicate – che ottimizzano localmente un singolo processo di sviluppo sulla base di un determinato criterio (quale l’alimentazione) – si stanno dimostrando sempre più spesso un ostacolo, piuttosto che un beneficio.

È verosimile che le novità più significative verranno dalle grandi organizzazioni disposte a fare investimenti consistenti. Si stima che per il solo passaggio ai FinFET da 20 nm e 14 nm, gli investimenti EDA si aggirino attorno al miliardo di dollari. Per le dimensioni dell’industria del settore, questo rappresenta uno sforzo importante ma indispensabile.

Il problema legato al signoff delle temporizzazioni può essere considerato come un microcosmo rappresentativo sia del cambiamento dell’industria EDA sia della sua evoluzione.

La soluzione a questo problema è rappresentato da Tempus Timing Signoff, un nuovo tool di analisi statica per la chiusura delle temporizzazioni di Cadence Design Systems capace di garantire una velocità superiore di un ordine di grandezza rispetto alle soluzioni tradizionali.

Benché alcune start-up abbiano sviluppato nuove tecnologie capaci di risolvere aspetti specifici del processo di signoff, il loro utilizzo da parte dei team di sviluppo di SoC (System-on-Chip) era precluso in quanto le tecnologie in questione non sono in grado di risolvere le problematiche di carattere complessivo.

Negli ultimi quindici anni, i fenomeni fisici tipici di tecnologie nanometriche hanno assunto un’importanza sempre più rilevante nel processo di sviluppo, originando una situazione ancora più complessa per quanto riguarda il signoff.

Il passaggio dalla progettazione ASIC alla progettazione SoC – avviatosi seriamente all’inizio del millennio – è stato accompagnato da un cambiamento radicale non solo nelle metodologie, ma anche nel modo in cui le tecnologie di progettazione più avanzate hanno fatto la loro comparsa sul mercato.

Solo quindici anni fa, il signoff dei progetti digitali era abbastanza diretto grazie all’uso di approssimazioni largamente condivise. In tale contesto, i ritardi di gate superavano largamente i ritardi di connessione, il cui contributo era praticamente trascurabile.

Il signoff era limitato principalmente all’esecuzione di un’analisi delle temporizzazioni, basata innanzitutto sui risultati forniti dal simulatore di gate ‘golden’ del costruttore ASIC. I team di progettazione hanno gradualmente sottratto una quota crescente della responsabilità di signoff ai fornitori di ASIC man mano che questi trasferivano la produzione alle fonderie.

Contemporaneamente, gli effetti dipendenti dal layout hanno iniziato a giocare un ruolo determinante nelle prestazioni del progetto. Sui percorsi critici, il peso dei ritardi di gate è invece diventato sempre meno importante. Parallelamente, i ritardi delle connessioni hanno assunto un ruolo chiave tra gli aspetti da considerare.

Ciò ha comportato l’avvento di una nuova generazione di tool – sviluppati sia dai grandi fornitori EDA sia dalle start-up – di tipo “layout-aware”.

Grazie alle tecnologie sviluppate, le start-up hanno indubbiamente giocato un ruolo cruciale. Esse hanno potuto colmare alcune carenze nell’offerta dei grandi fornitori, ricavando da un selezionato gruppo di “clienti segnalatori” fornire informazioni vitali sulle prestazioni dei tool utilizzati nei progetti reali.

Effetti nanometrici

Negli ultimi anni, molti degli effetti nanometrici con cui si sono dovuti confrontare i team di progettazione SoC sono divenuti sempre più intercorrelati. Solo dieci anni fa, una violazione di timing su un cammino critico poteva essere facilmente risolta inserendo un buffer o spostando dei gate per ridurre la distanza di connessione, e con essa il ritardo. Un tool specifico, ottimizzato per fornire l’analisi e la relativa soluzione, poteva essere facilmente inserito in un flusso di sviluppo più ampio.

L’analisi era spesso ottimizzata in funzione della capacità, piuttosto che dell’accuratezza. A causa dell’evoluzione verso i progetti da milioni di gate, i carichi legati ai tempi di esecuzione costituivano spesso la problematica principale.

Gli effetti parassiti potevano – in larga parte – essere espressi in forma astratta, ad eccezione dei cammini con prestazioni prossime ai margini di timing ammessi.

A 130 nm, per esempio, il gap tra linee di connessione metalliche è tale che le capacità di accoppiamento sono mascherate dalle capacità parassite di pin e masse. Per le capacità di accoppiamento inter-traccia, è addirittura più semplice e rapido prevedere un piccolo margine aggiuntivo.

Anche il numero di cicli di analisi delle temporizzazioni era piuttosto limitato. In generale, era sufficiente analizzare gli scenari riguardanti il caso migliore, i valori nominali e il caso peggiore, concentrandosi su tre parametri chiave: processo, tensione e temperatura.

Questo approccio consentiva di coprire tutte le condizioni operative realistiche del progetto in funzione del processo utilizzato. In tale contesto era ragionevole ritenere che il ritardo più critico si sarebbe verificato in condizioni di massima temperatura, minima tensione e processo più sfavorevole.

Con la riduzione delle geometrie, le convinzioni date per scontate hanno iniziato a venire meno. A 65 nm, per esempio, la capacità di accoppiamento tra interconnessioni metalliche assume un peso significativo poiché la distanza tra le linee si riduce mentre l’altezza delle tracce aumenta per tenere la resistenza parassita sotto controllo. Come risultato, le linee iniziano a comportarsi in modo simile alle superfici parallele di un condensatore.

A 45 nm, la variazione dello spessore metallico diventa un problema fondamentale, comportando un incremento del range su cui eseguire la simulazione e fornire i valori dei ritardi “best-case” e “worst-case”.

Al di sotto dei 45 nm, le variazioni legate al processo litografico di transistor, gate e strutture locali d’interconnessione assumono un peso significativo, implicando l’introduzione di margini più consistenti per accogliere tutta la gamma di variazioni di processo.

Altri effetti, più sottili, legati al passaggio alle dimensioni nanometriche hanno contribuito ad aumentare notevolmente gli sforzi necessari per ottenere il signoff delle temporizzazioni.

Il tema generale rimane quello dell’interazione tra effetti globali e locali. Sin dall’inizio dello scorso decennio, il comportamento al variare delle condizioni termiche è diventato sempre più difficile da prevedere a causa di un fenomeno denominato “dipendenza dall’inversione termica”.

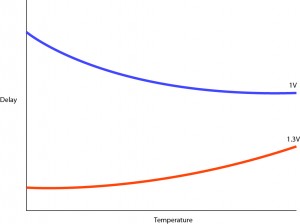

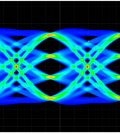

Tale comportamento è legato dall’uso di tensioni di alimentazione più basse, le quali permettono di ottenere una maggiore efficienza energetica (Fig. 1). Invece di girare più velocemente, al di sotto di determinate soglie di tensione e al diminuire della temperatura la circuiteria lavora più lentamente: tale effetto dipende dalla soglia utilizzata dai dispositivi che si trovano sul percorso da analizzare. La ragione di questo comportamento è legata al fatto che due effetti si combinano per determinare il ritardo introdotto da un gate logico. Alle tensioni utilizzate tradizionalmente, la mobilità controlla la corrente di drain di un transistor attivo. Quando la tensione cala, la tensione di soglia assume un peso maggiore nei determinare la corrente di drain. Da quui l’esigenza di nuove ed esaustive analisi.

Nei processi nanometrici, la variabilità è più localizzata rispetto ai vecchi processi. L’ampiezza delle linee metalliche è talmente ridotta da condizionare la resistenza del collegamento con variazioni minime. Essendo la metallizzazione un processo distinto dal trattamento dello strato base, non è possibile dare per scontato che le variazioni di processo si manifestino nello stesso modo in entrambi gli strati. Pertanto, a 45 nm (e in misura maggiore a 28 nm), per ottenere analisi e ottimizzazioni corrette dei tempi, sono necessari più punti di estrazione.

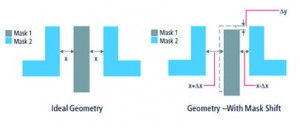

Nei processi sub-28 nm la tecnologia di double patterning introduce altri elementi di variabilità. Poiché la litografia in double patterning implica l’uso di due maschere per uno stesso strato, è necessario garantire un allineamento preciso, in modo tale che le spaziature tra pattern siano omogenee su tutto il die. Benché le fonderie stiano lavorando alacremente per minimizzare l’effetto, vi saranno sempre degli sfasamenti nelle maschere la cui l’entità potrebbe essere impossibile da prevedere (Fig. 2). Per riflettere l’impatto degli sfasamenti nelle varie direzioni in funzione di una data combinazione tra temperatura, tensione e altre variabili di processo, sono richieste nuove rappresentazioni temporali.

Progettazione a basso consumo

La crescente attenzione verso gli sviluppi low-energy implica livelli di complessità aggiuntivi nel signoff delle temporizzazioni.

Nei progetti che utilizzano tecniche innovative – quali l’adattamento dinamico di frequenza e tensione per ottimizzare l’efficienza energetica – dovranno essere analizzate varie condizioni operative, garantendo così che effetti quali l’IDT (inverted Temperature dependance) non influenzino negativamente l’affidabilità temporale del SoC.

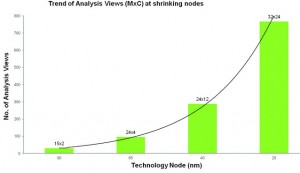

Tali analisi devono essere eseguite in relazione ad altre fonti di variabilità, con un aumento esponenziale delle possibili combinazioni. Considerando un insieme di otto modalità operative, è facile raggiungere situazioni in cui è necessario analizzare più di 200 rappresentazioni temporali. Attraverso un’attenta selezione e una riduzione delle combinazioni – eliminando quelle che probabilmente non daranno risultati significativamente diversi rispetto ad altri test – è possibile contenerne il numero.

Comunque sia, il team di implementazione del SoC deve sempre confrontarsi con un’enorme mole di rappresentazioni temporali (Fig. 3). Il problema non è limitato ai processi all’avanguardia. Sempre più spesso, le tecniche di progettazione low-power vengono applicate anche ai progetti destinati ai processi più datati. Benché questi processi siano caratterizzati da un numero più limitato di elementi di variabilità, man mano che le tensioni vengono ridotte (per sfruttare i vantaggi del risparmio energetico), effetti quali l’IDT diventano più rilevanti.

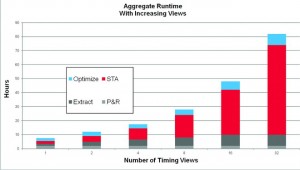

Il tempo necessario per generare le varie rappresentazioni temporali costituisce solo una piccola parte del problema. Oggi, fino al 40% del flusso di realizzazione di un chip è legato alle attività sui risultati delle analisi (Fig. 4). Ogni rappresentazione temporale genera un set di violazioni che deve essere correlato ai risultati di altre rappresentazioni temporali. Il consolidamento dei dati richiede tempo, indagini ingegneristiche e – per molti team – script personalizzati per elaborare le informazioni.

La chiusura delle temporizzazioni

Vi è poi il problema mettere a punto i cambiamenti necessari per “chiudere” le temporizzazioni. Gli attuali tool di signoff i non si occupano dell’aspetto fisico. Qualsiasi cambiamento – per esempio l’inserimento di un buffer – è lasciato all’ambiente di implementazione e viene effettuato in una fase di processo successiva, dopo la generazione di un ECO (engineering change order).

Poiché nei progetti molto popolati è difficile trovare dello spazio libero, il placement di nuove celle spesso genera risultati notevolmente differenti rispetto a quanto ipotizzato dagli algoritmi di ottimizzazione. Ciò comporta un significativo disallineamento tra gli effetti parassiti di interconnessione previsti durante le fasi di ottimizzazione e quelli successivi al placement e al routing che scaturiscono dall’ECO.

Le variazioni possono influenzare la temporizzazione di cammini già validati a livello di timing, con una violazione nella rappresentazione temporale che si manifesta a partire dalle iterazioni successive. In sostanza, ciò che prima poteva essere una rappresentazione temporale “pulita”, dopo il placement e il re-routing potrebbe contenere numerose violazioni.

Dall’analisi del modo in cui il signoff delle temporizzazioni è evoluto nell’ultimo decennio, emerge chiaramente un aspetto. Per risolvere i problemi non è sufficiente un semplice aggiornamento tecnologico.

L’approccio classico prevede che siano le start-up a originare gran parte dell’innovazione dei mercati più strettamente legati alle alte tecnologie. In realtà le startup si appoggiano tradizionalmente a una particolare tipologia di clienti (segnalatori) per sviluppare delle soluzioni pronte per l’introduzione sul mercato.

Tali soluzioni però non sempre sono adatte al mercato in quanto l’esigenza attuale è poter disporre di tool non più puntuali, bencì capaci di coprire in modo trasversale tutte le fasi del flusso di implementazione. Benché un engine di implementazione più accurato consenta di ridurre alcuni degli overhead legati all’analisi di molte rappresentazioni temporali, la vera soluzione è analizzare vari punti di quel flusso, con un approccio più solistico.

Benché una soluzione specifica possa avere molti punti di forza e possa garantire un miglior supporto per determinate problematiche, oggi è essenziale disporre di tutta la tecnologia necessaria per mettere a punto una proposta più coesa.

Ciò prevede la gestione degli input provenienti da fonderie e IDM, che possono vantare competenze sugli elementi di variabilità che influenzano le temporizzazioni. Inoltre, anche i fornitori di librerie giocano un ruolo importante nella comprensione sia dei problemi legati all’evoluzione verso geometrie ridotte sia dell’impatto di tecnologie quali il double patterning. A questo si sommano i clienti pilota, i quali possono contribuire con esempi concreti capaci di sollecitare tutte le parti di un flusso di sviluppo. Inoltre, non è da trascurare il ruolo dei fornitori di tool EDA, esperti nel raccogliere tutti gli input e nello sviluppare nuovi modi per gestire l’afflusso dei dati.

I fornitori devono avere come obiettivo quello di considerare il flusso di sviluppo in modo interdisciplinare e di capire quali siano i punti che limitano la velocità del progetto. Un engine di implementazione più accurato per gli ECO rappresenta una delle possibili risposte al tema del signoff delle temporizzazioni.

Ma l’approccio più efficace è quello di considerare le specifiche generali del signoff e trovare modalità di applicazione dei correttivi e degli ECO più integrate possibile al processo di signoff stesso. Ciò richiede la combinazione di nuove tecnologie e un’attenzione particolare verso i dettagli architetturali del flusso nella loro globalità, due aspetti che sono un player con decenni di esperienza nel campo dell’implementazione può garantire.

Come risultato, l’industria sta evolvendo verso una nuova linea di sviluppo che prevede una matrice completa di partnership, e non dei semplici collegamenti individuali o dei gruppi dedicati alla progettazione di singoli tool. Considerando tutti questi aspetti è evidente come i fornitori di tool EDA possono reagire molto più rapidamente alle nuove esigenze di sviluppo, rispecchiando più fedelmente il ritmo d’innovazione in atto nella progettazione di prodotto e nell’ingegneria di processo.

Chi-Ping Hsu, senior vp, research and development silicon realization group, Cadence Design Systems

Contenuti correlati

-

I semiconduttori nel settore medicale

In questo articolo faremo una panoramica sul ruolo crescente dei semiconduttori nel settore sanitario Leggi l’articolo completo su EO Medical27

-

Il futuro dei semiconduttori visto da Canon

Canon supporta i produttori di semiconduttori da quasi cinquant’anni, fornendo apparecchiature all’avanguardia per la fotolitografia. Il Gruppo progetta e produce in Giappone oltre alle macchine per la fotolitografia, anche attrezzature ad alto vuoto per la deposizione di...

-

Cadence ha presentato la piattaforma Millennium

Cadence Design Systems ha annunciato Cadence Millennium Enterprise Multiphysics Platform. Si tratta di una soluzione Digital Twin accelerata hardware/software destinata alla progettazione e all’analisi di sistemi multifisici. Questa soluzione chiavi in mano include unità di elaborazione grafica...

-

La nuova piattaforma Celsius Studio di Cadence migliora la convergenza ECAD/MCAD

Cadence Design Systems ha presentato Cadence Celsius Studio, una soluzione completa nell’ambito della progettazione e dell’analisi termica per sistemi elettronici basata sulla Intelligenza Artificiale (AI). Celsius Studio è una piattaforma unificata destinata all’analisi in campo termico dei...

-

Cadence ha ampliato il supporto per lo standard 3Dblox 2.0

Cadence Design Systems ha annunciato la disponibilità di nuovi flussi di prototipazione di sistema basati sulla piattaforma Cadence Integrity 3D-IC in grado di supportare lo standard 3Dblox 2.0. I flussi sono stati inoltre ottimizzati per tutte le...

-

Cadence espande la licenza di Pfizer al software di molecular design

Cadence Molecular Sciences (OpenEye), una business unit di Cadence, ha annunciato che Pfizer ha firmato un accordo per estendere ed espandere l’accesso ai prodotti Cadence e ai kit di strumenti di programmazione per la progettazione molecolare avanzata....

-

Cadence amplia il portafoglio IP per il processo TSMC N3E

Cadence Design Systems ha ampliato la sua offerta di IP di progettazione estendendola al processo a 3 nm di TSMC (N3E). Queste soluzioni mettono a disposizione dei clienti un’ampia gamma di IP di memoria e interfacce ad...

-

Virtuoso Studio Cadence supporta i flussi di riferimento RF e mmWave per i processi di TSMC

Cadence Design Systems ha collaborato con TSMC per integrare la nuova versione di Virtuoso Studio nei flussi di riferimento N16 mmWave e N6RF di TSMC. La società ha anche annunciato il supporto aggiuntivo per il flusso di...

-

Cadence presenta l’ottava generazione della piattaforma Tensilica Xtensa LX

Cadence Design Systems ha presentato Xtensa LX8, l’ottava generazione della piattaforma Tensilica Xtensa LX. Il processore Xtensa LX8 offre nuove funzionalità progettate per soddisfare le crescenti necessità di prestazioni a livello di sistema e i requisiti per...

-

Ottimizzare elaborazione, rilevamento e controllo general purpose con le MCU Arm Cortex-MO+

Le MCU MSPM0 Arm Cortex-M0+ proposte da Texas Instruments offrono ai progettisti maggiori opzioni, più flessibilità di progettazione e una gamma più ampia di software e strumenti intuivi Leggi l’articolo completo su EO 512